我们来详细讲解一下半导体制造中的“刻蚀(Etch)”工艺技术。

"什么是刻蚀(Etch)?"

刻蚀是半导体制造过程中一项至关重要的、普遍存在的物理或化学过程。它的核心目标是在半导体晶圆(Wafer)的表面,根据设计图形,"精确地去除"不需要的材料层(通常是几纳米到几微米厚的薄膜,如二氧化硅、氮化硅、金属等),从而形成特定的几何结构,如导线(Lines)、接触孔(Contacts)、沟槽(Trenches)、深沟(Vias)等。

可以将其想象成在材料上“雕刻”或“腐蚀”出所需图案的过程。它是与“沉积(Deposition)”工艺相对应的步骤,沉积是添加材料,而刻蚀是移除材料。

"刻蚀的重要性"

刻蚀工艺的质量直接决定了半导体器件的性能和可靠性。其重要性体现在:

1. "图形转移(Pattern Transfer):" 将光刻(Lithography)步骤中形成的微细图形精确地转移到下方的材料层上。

2. "形成微细结构:" 制造器件所需的各种三维结构,如晶体管栅极、互连线、绝缘层中的接触孔、存储单元的电容结构等。

3. "尺寸控制:" 精确控制最终形成的器件尺寸和特征尺寸。

4. "层间连接:" 通过刻蚀接触孔,

相关内容:

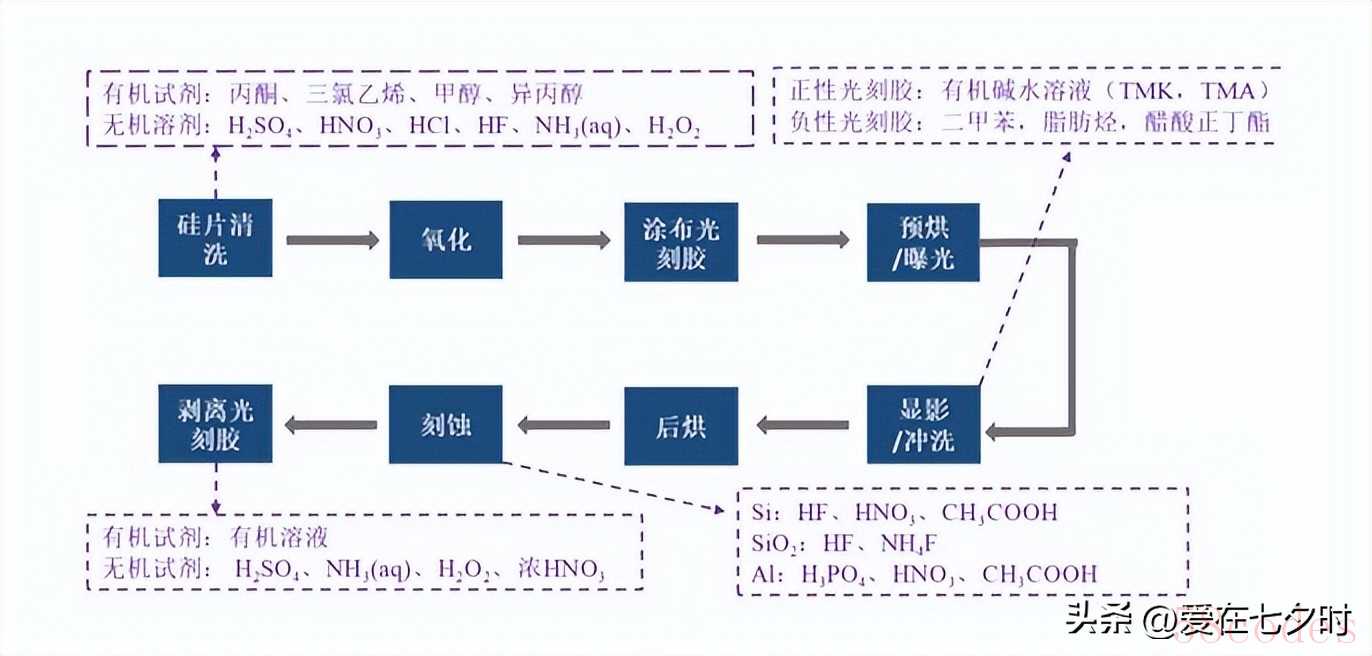

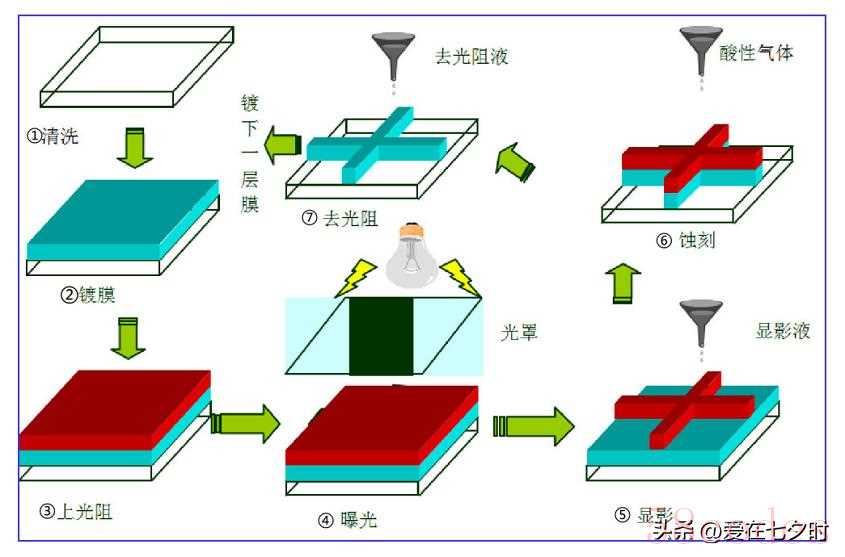

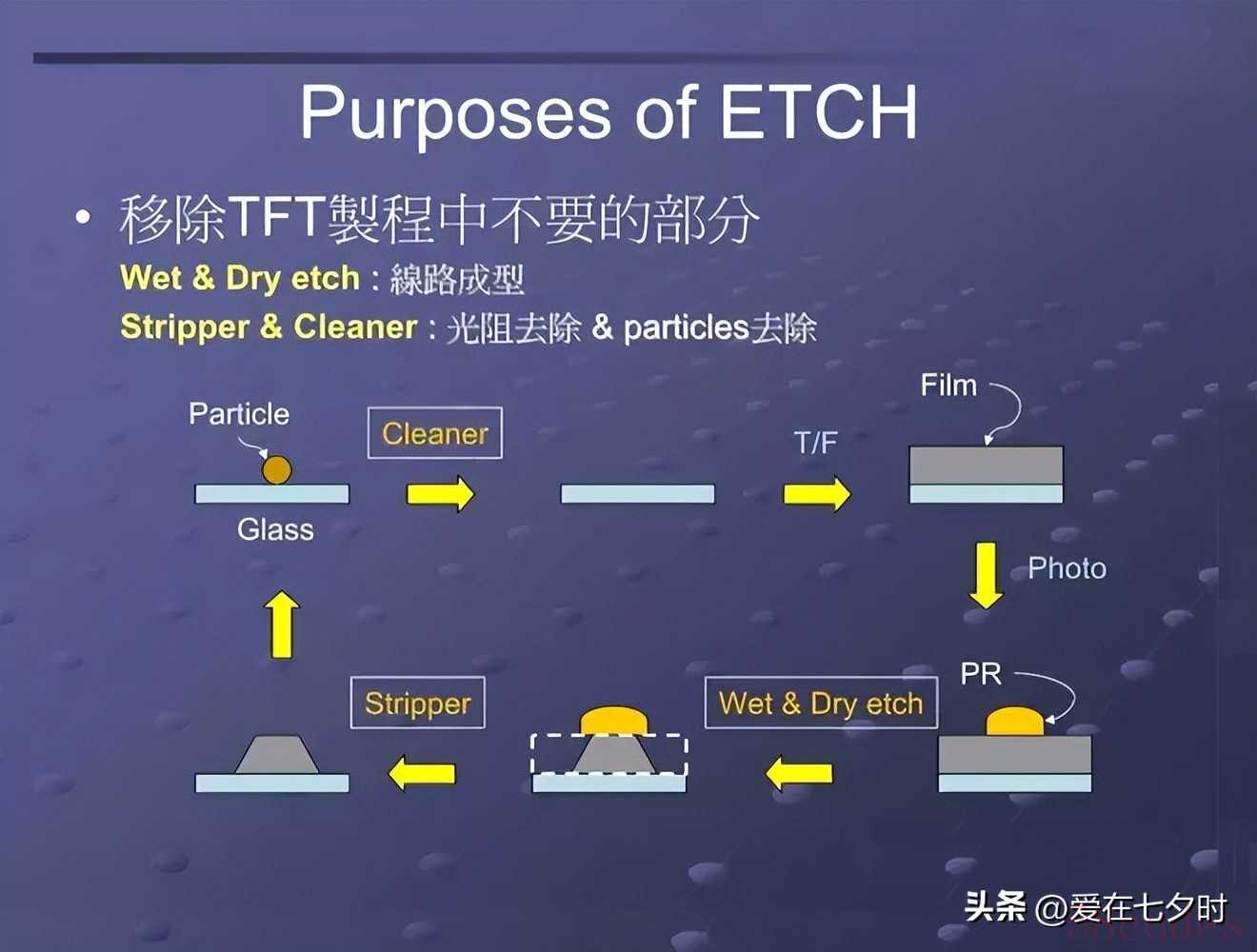

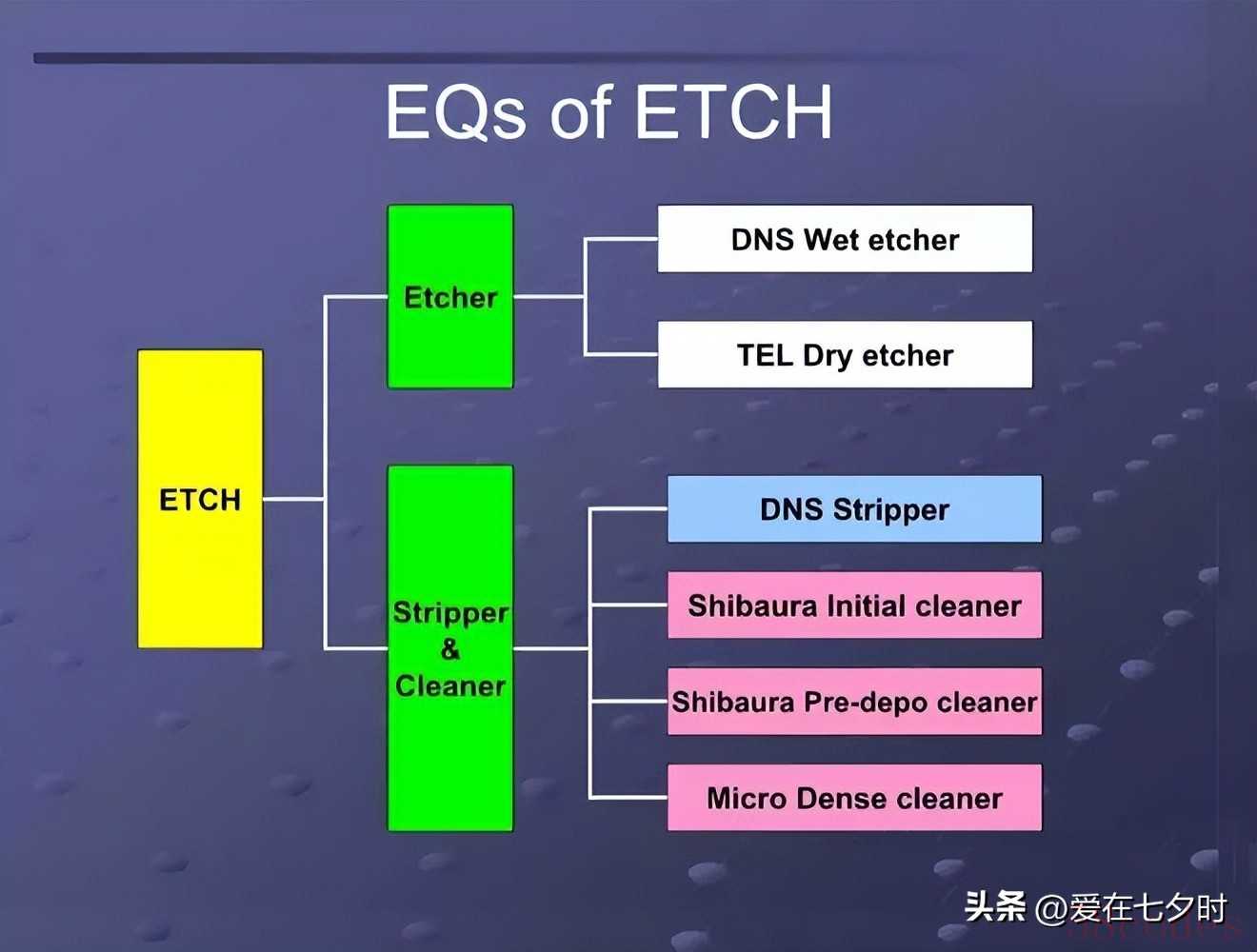

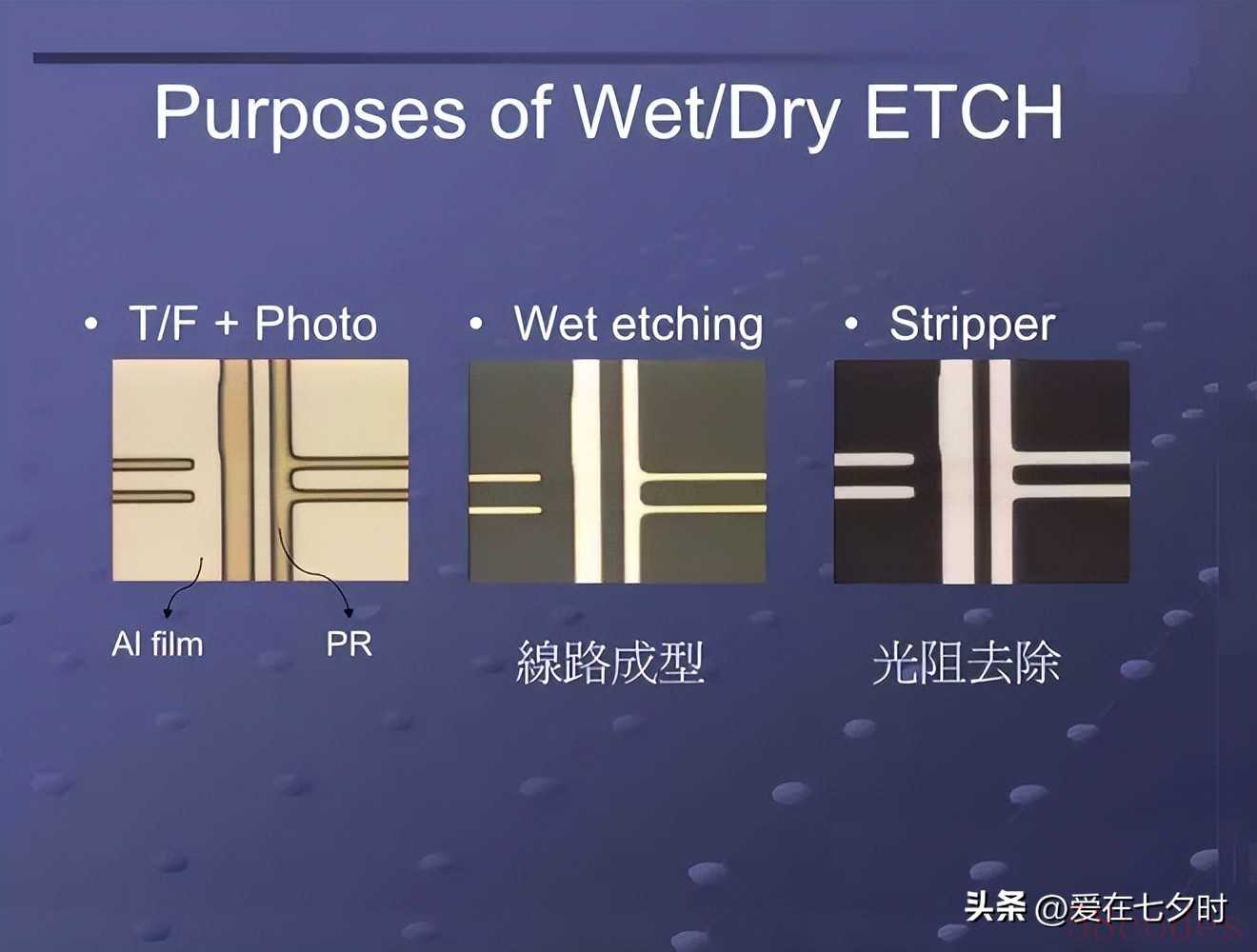

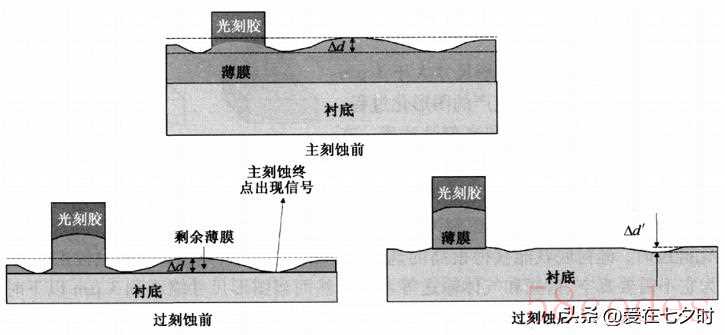

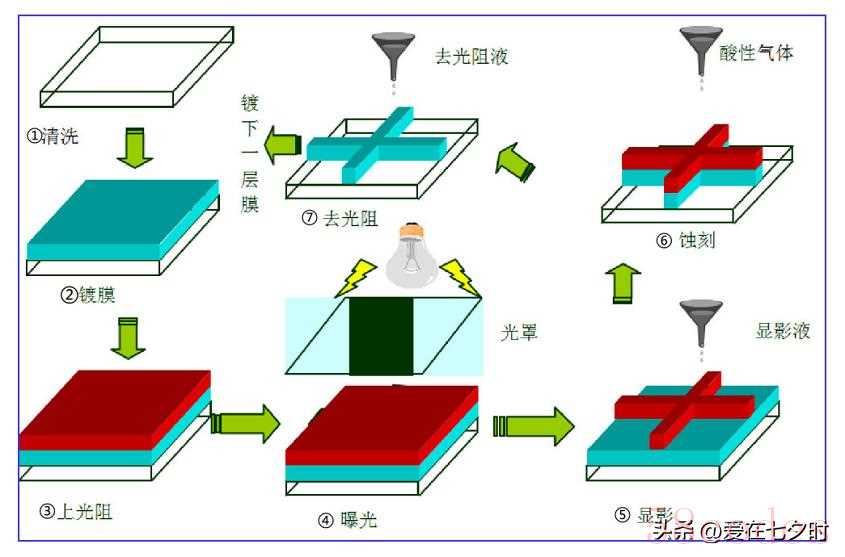

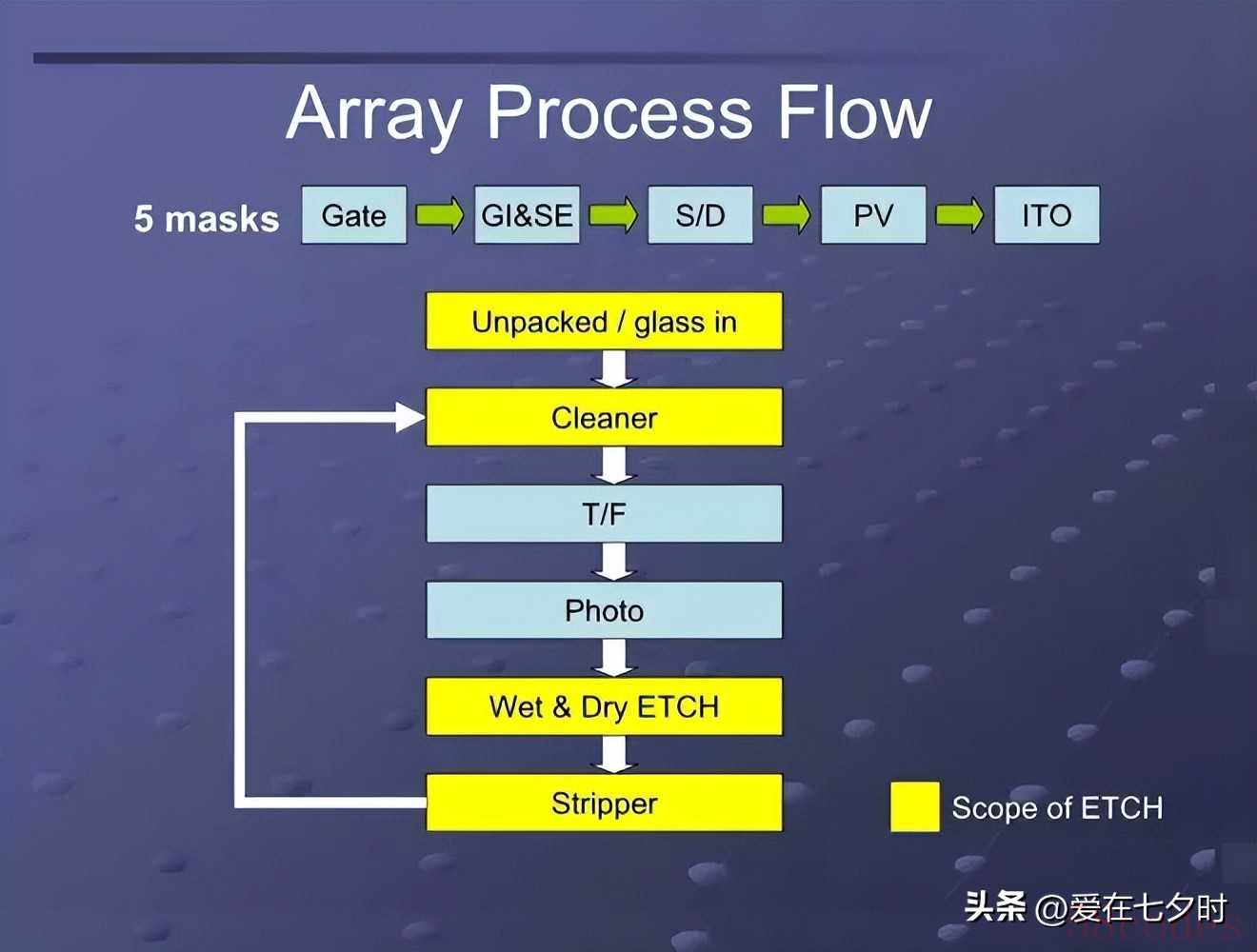

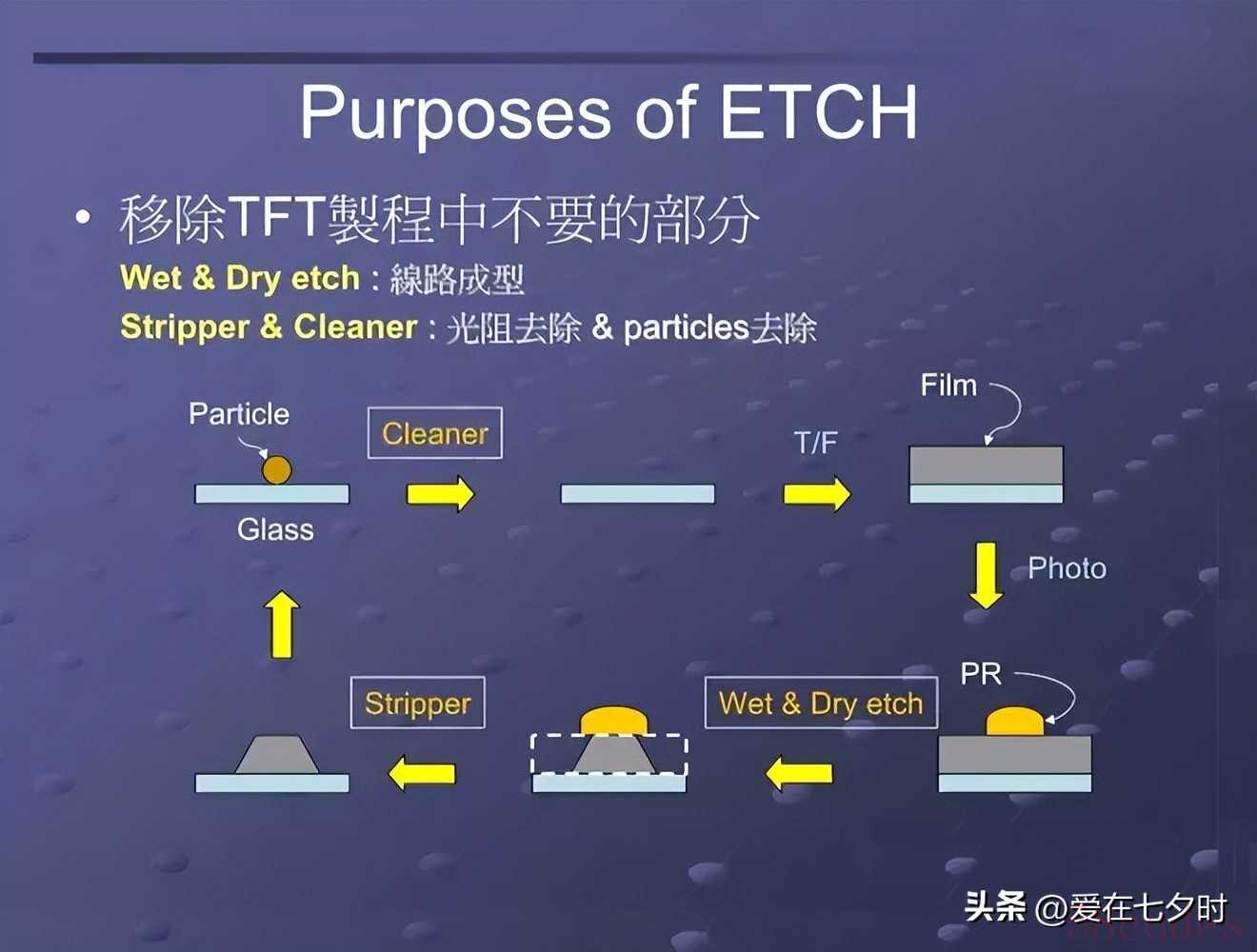

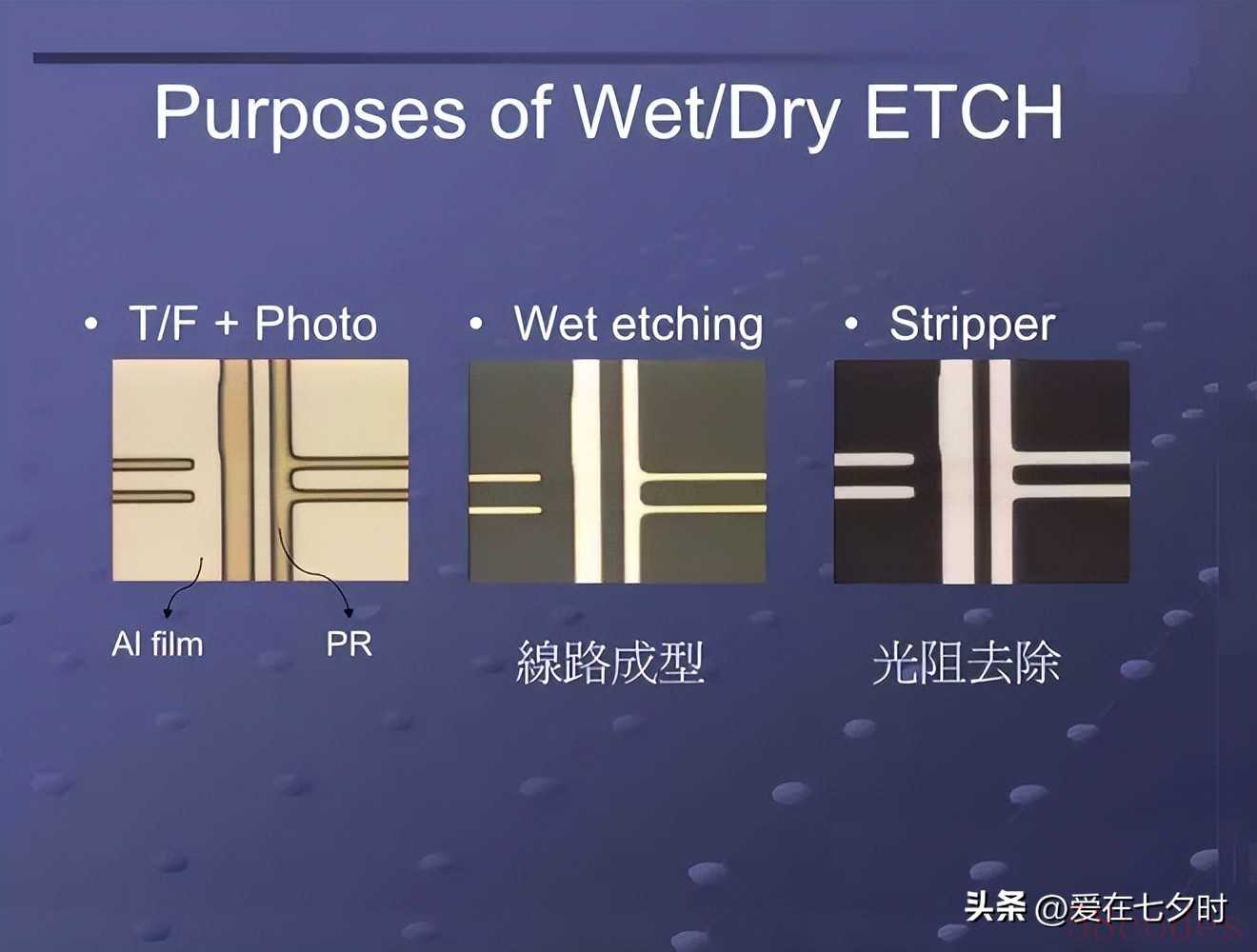

内外行的朋友都知道:半导体制造过程复杂,工艺流程颇多,特别是前道的“流片”,更是繁琐中的繁琐。本章节要跟大家分享的就是关于“刻蚀”工艺,讲到“刻蚀”工艺我想到一篇古文《核舟记》,描写了一个微雕:“通计一舟,为人五;为窗八;为箬篷,为楫,为炉,为壶,为手卷,为念珠各一;对联、题名并篆文,为字共三十有四;而计其长曾不盈寸。盖简桃核修狭者为之。嘻,技亦灵怪矣哉!”想想觉得和芯片制造中“刻蚀”有着异曲同工之妙!在完成显影检查的步骤之后,掩模版的图形就被固定在光刻胶膜上;刻蚀就是通过物理或者化学手段将晶圆表面未被光刻胶保护的材料去除,将掩膜版图形转移到基材的工艺。 一、“刻蚀”工艺的介绍刻蚀,英文为Etch,它是半导体制造工艺,微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。是与光刻相联系的图形化(pattern)处理的一种主要工艺。所谓刻蚀,实际上狭义理解就是光刻腐蚀,先通过光刻将光刻胶进行光刻曝光处理,然后通过其它方式实现腐蚀处理掉所需除去的部分。刻蚀是用化学或物理方法有选择地从硅片表面去除不需要的材料的过程,其基本目标是在涂胶的硅片上正确地复制掩模图形。随着微制造工艺的发展,广义上来讲,刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称,成为微加工制造的一种普适叫法。

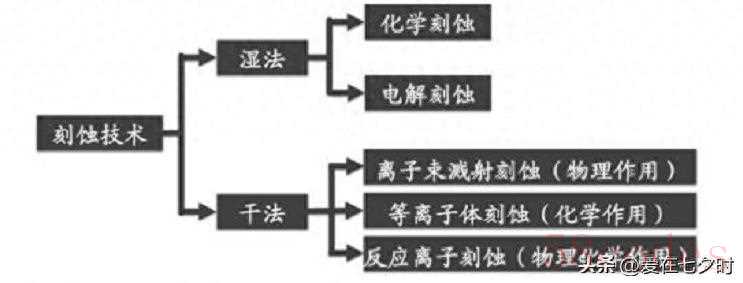

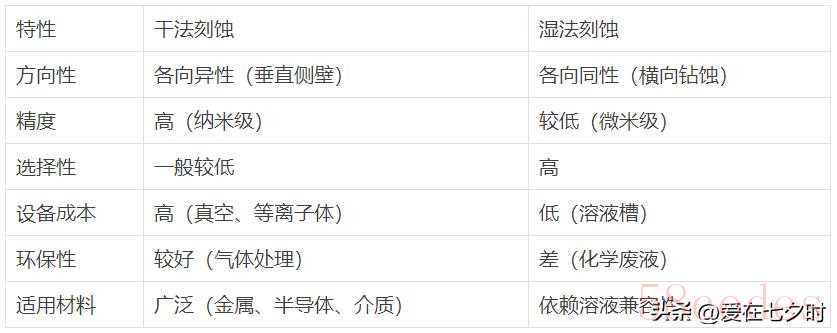

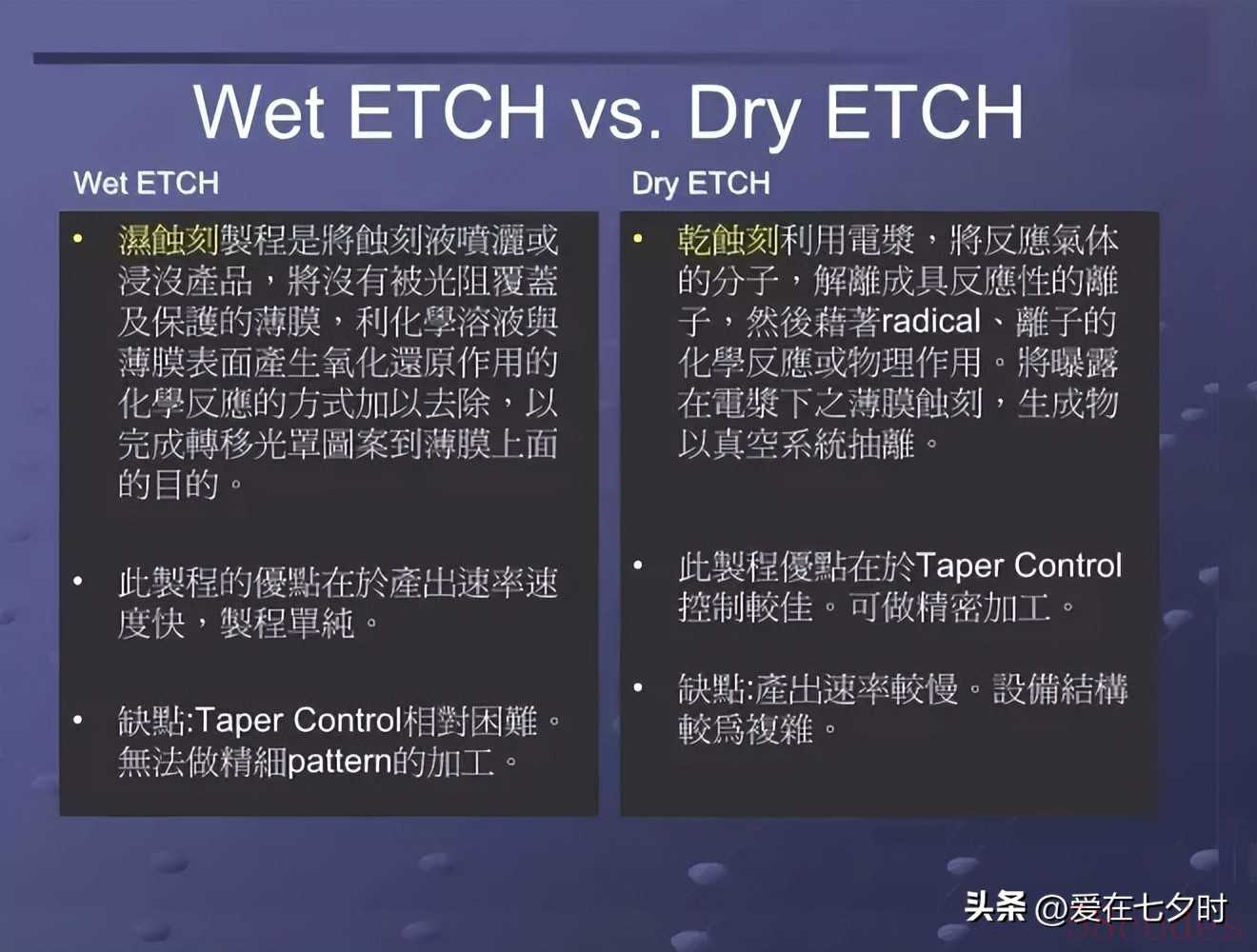

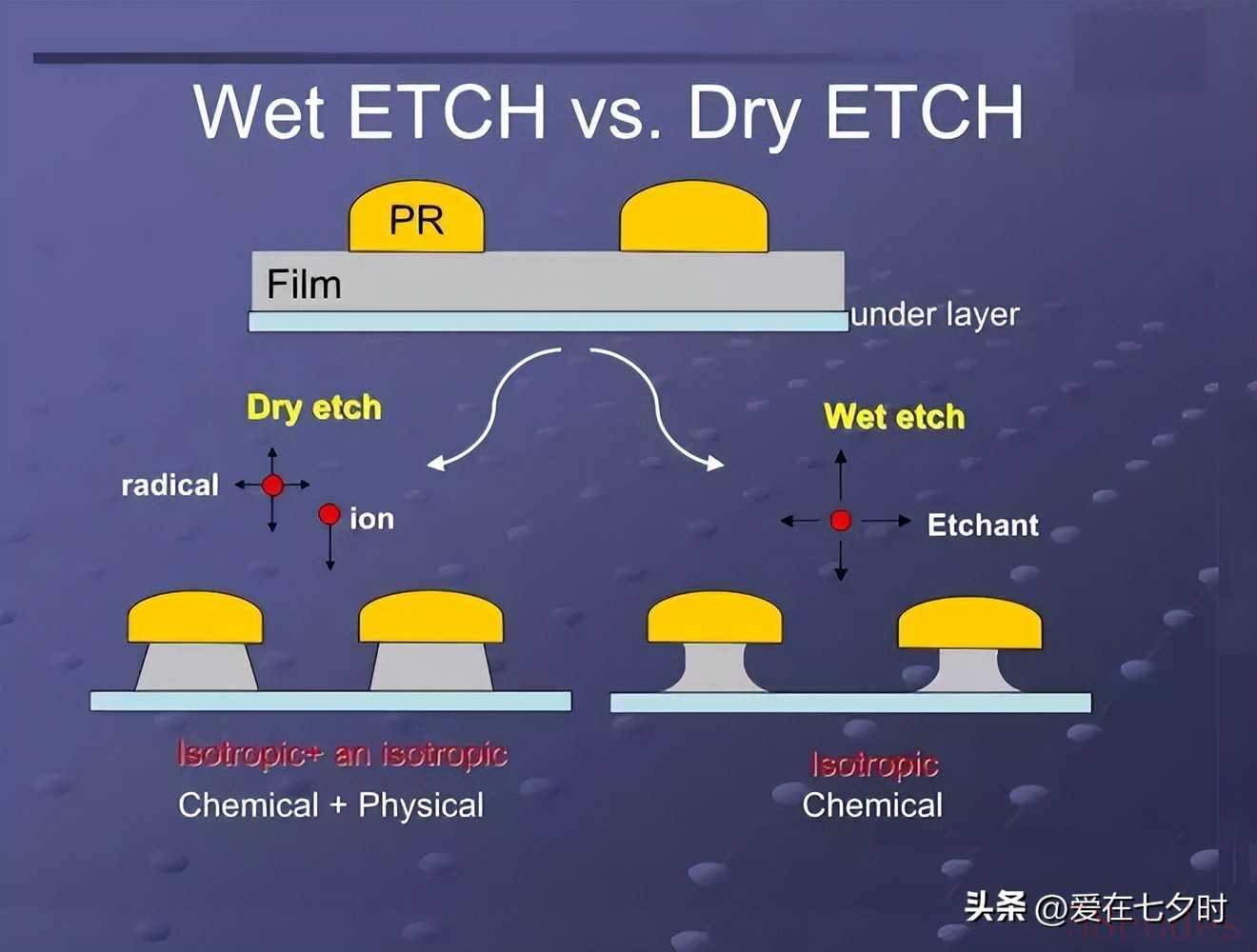

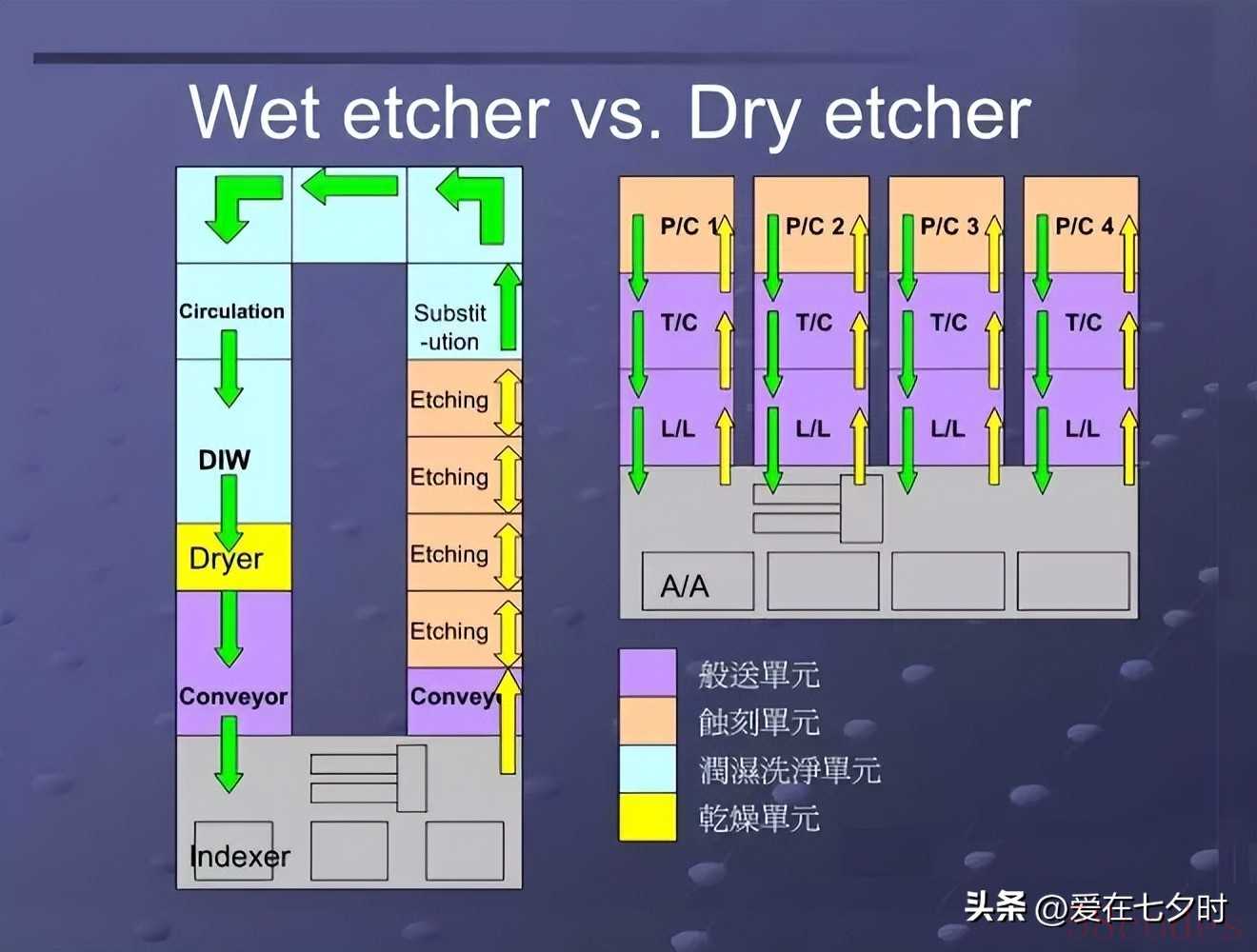

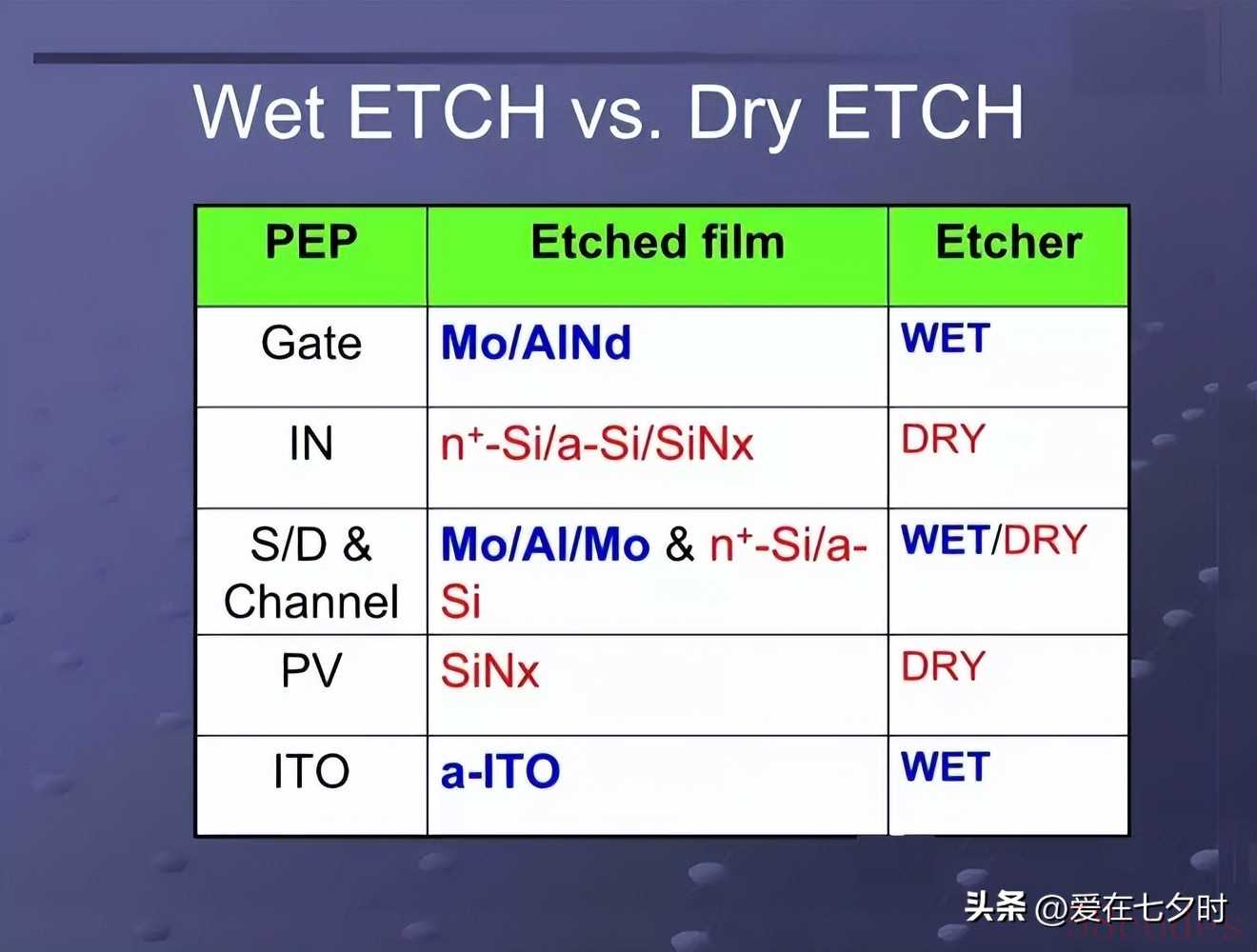

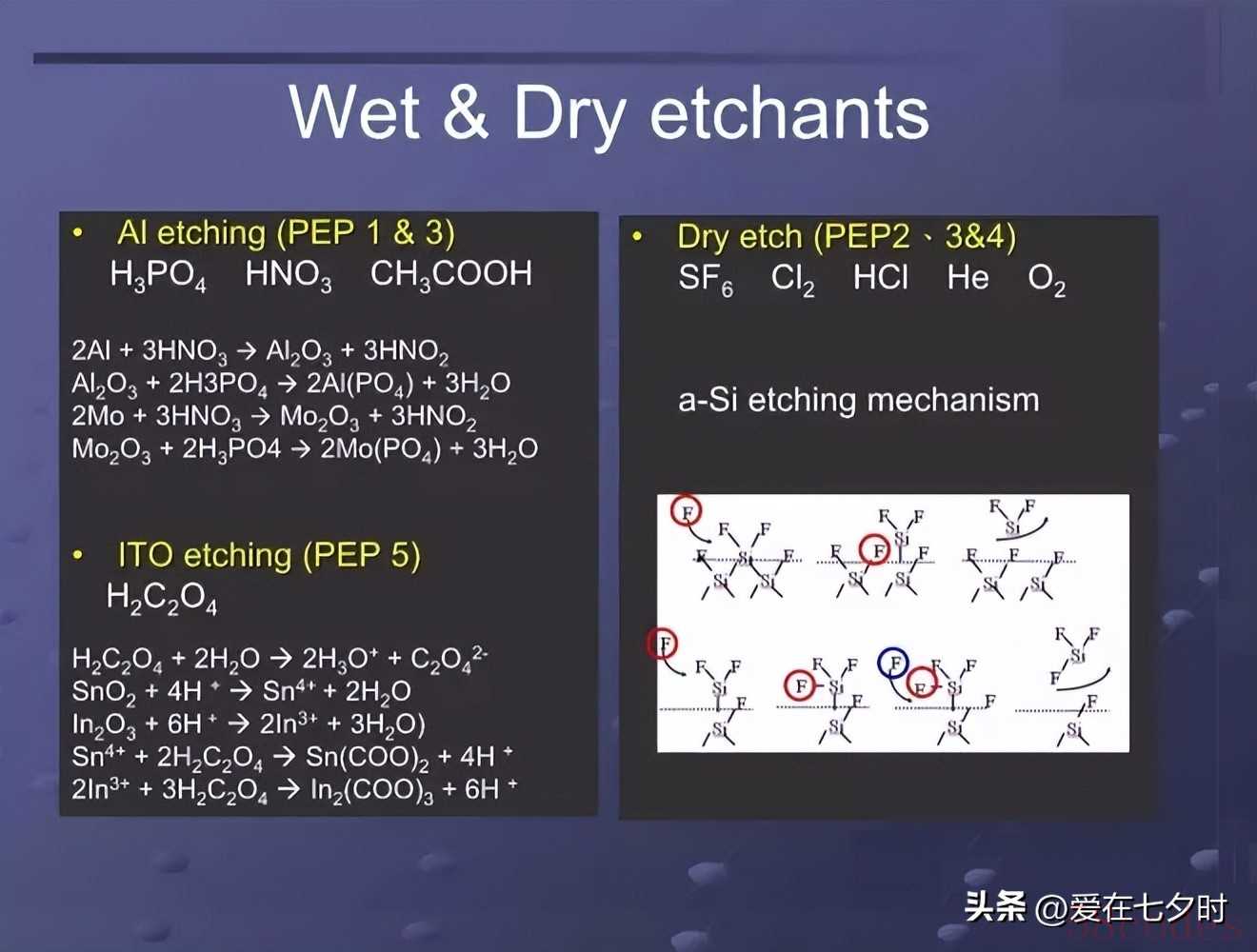

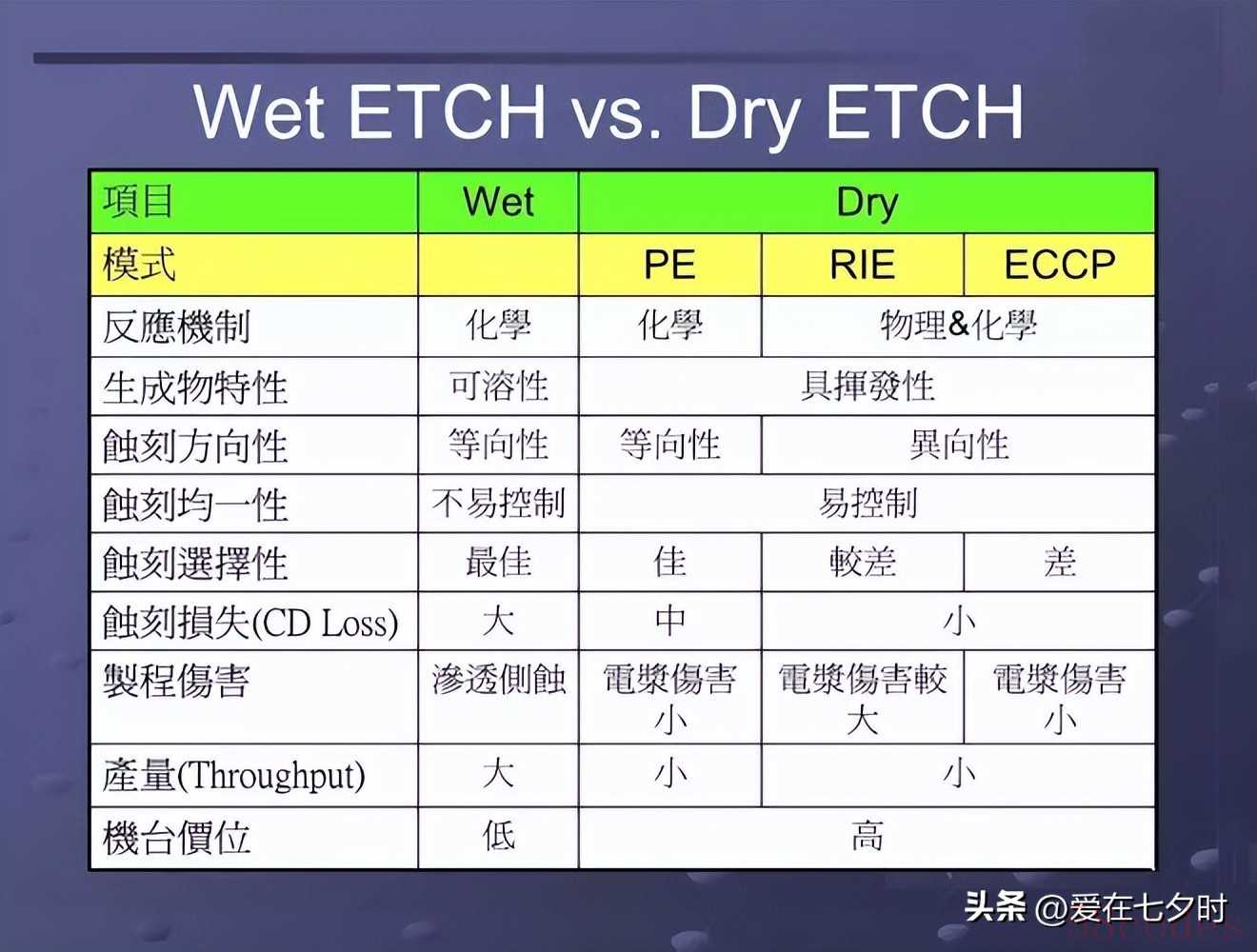

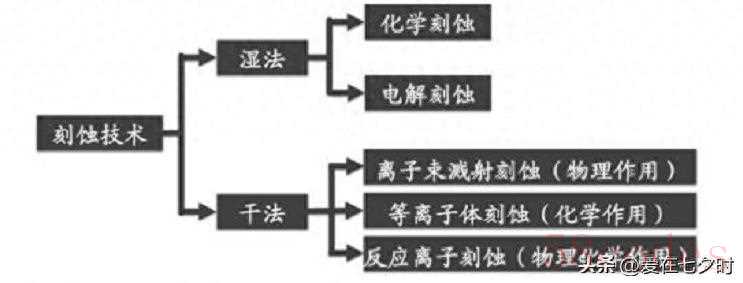

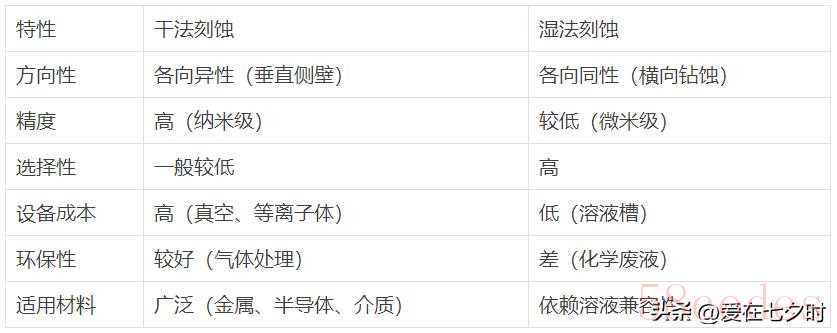

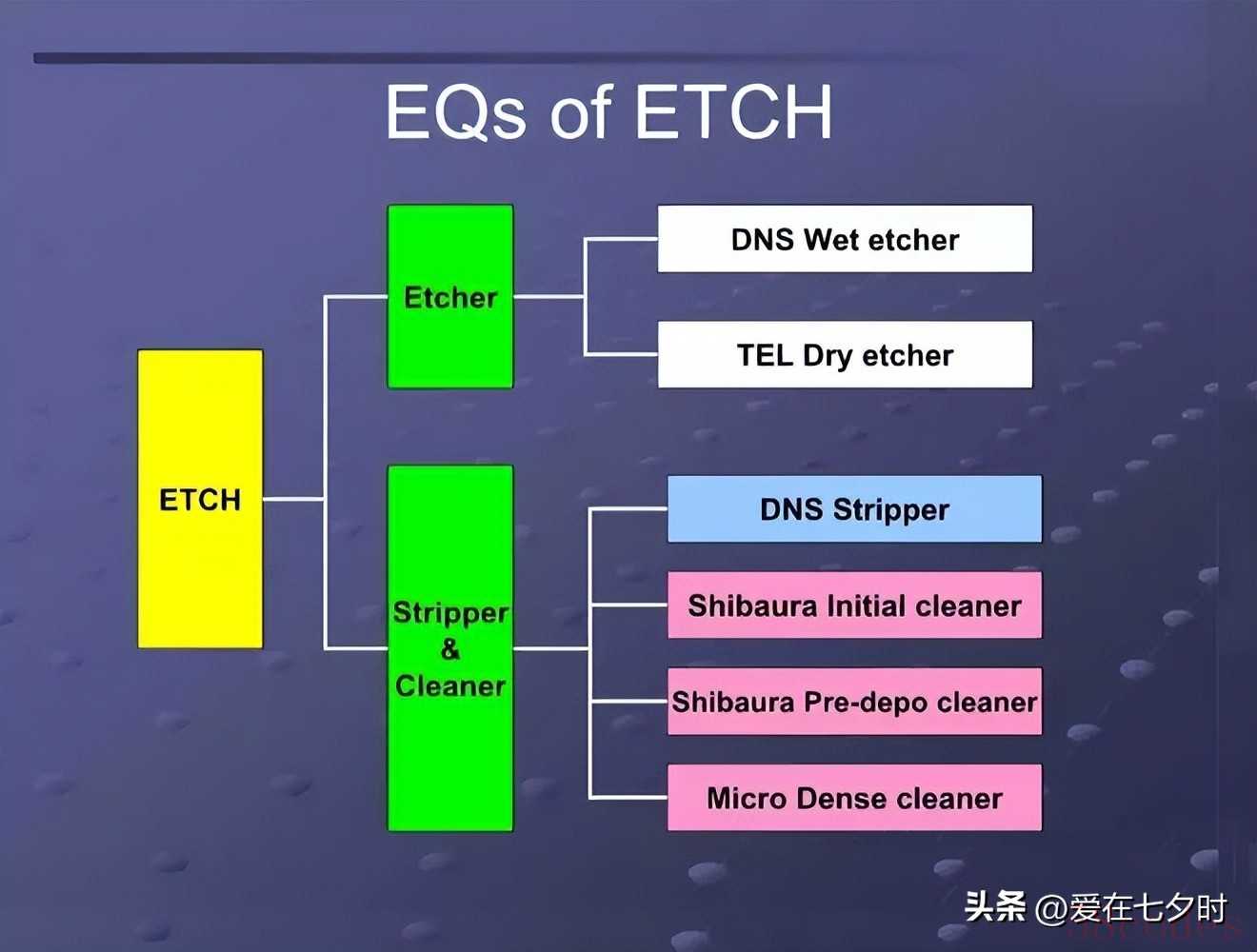

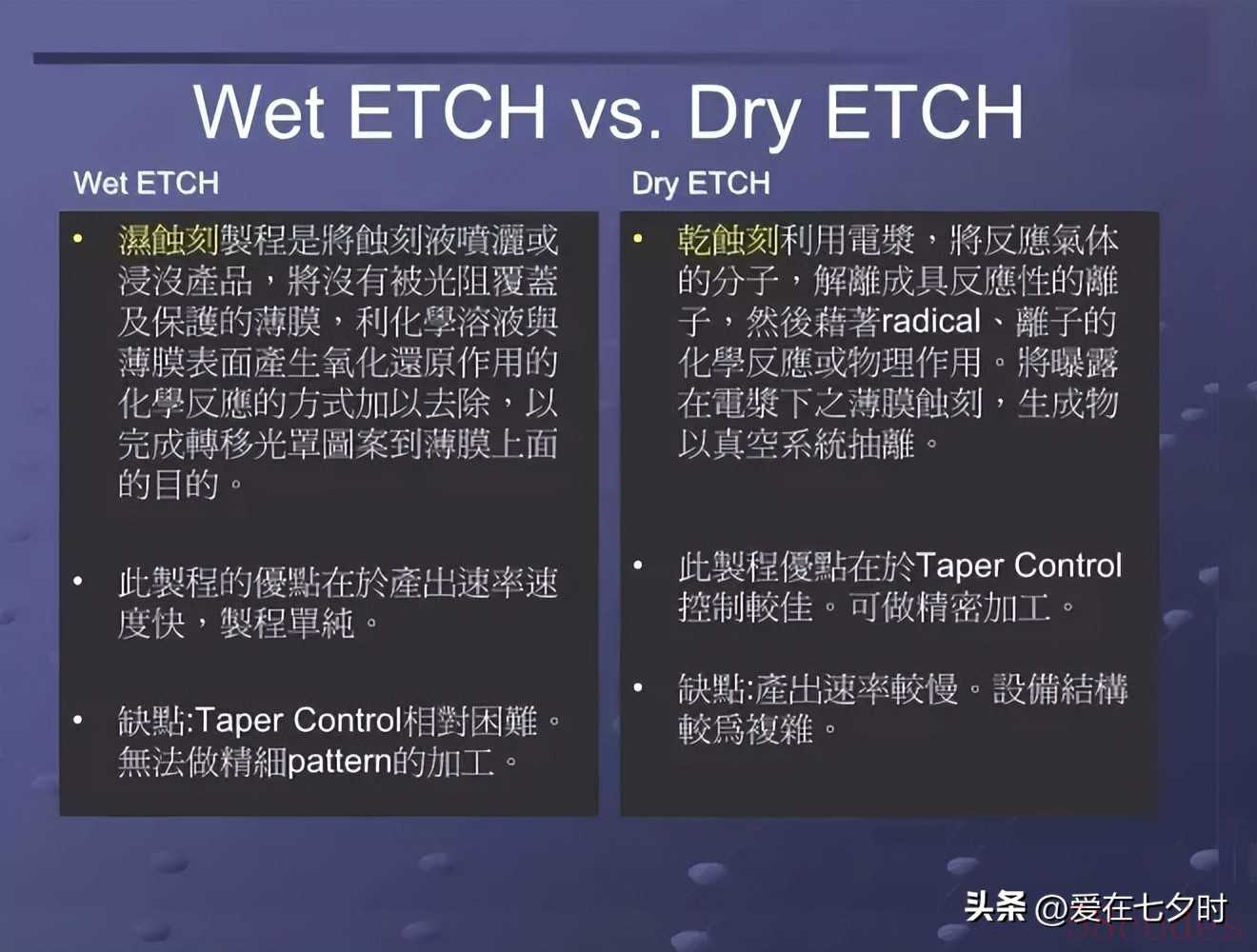

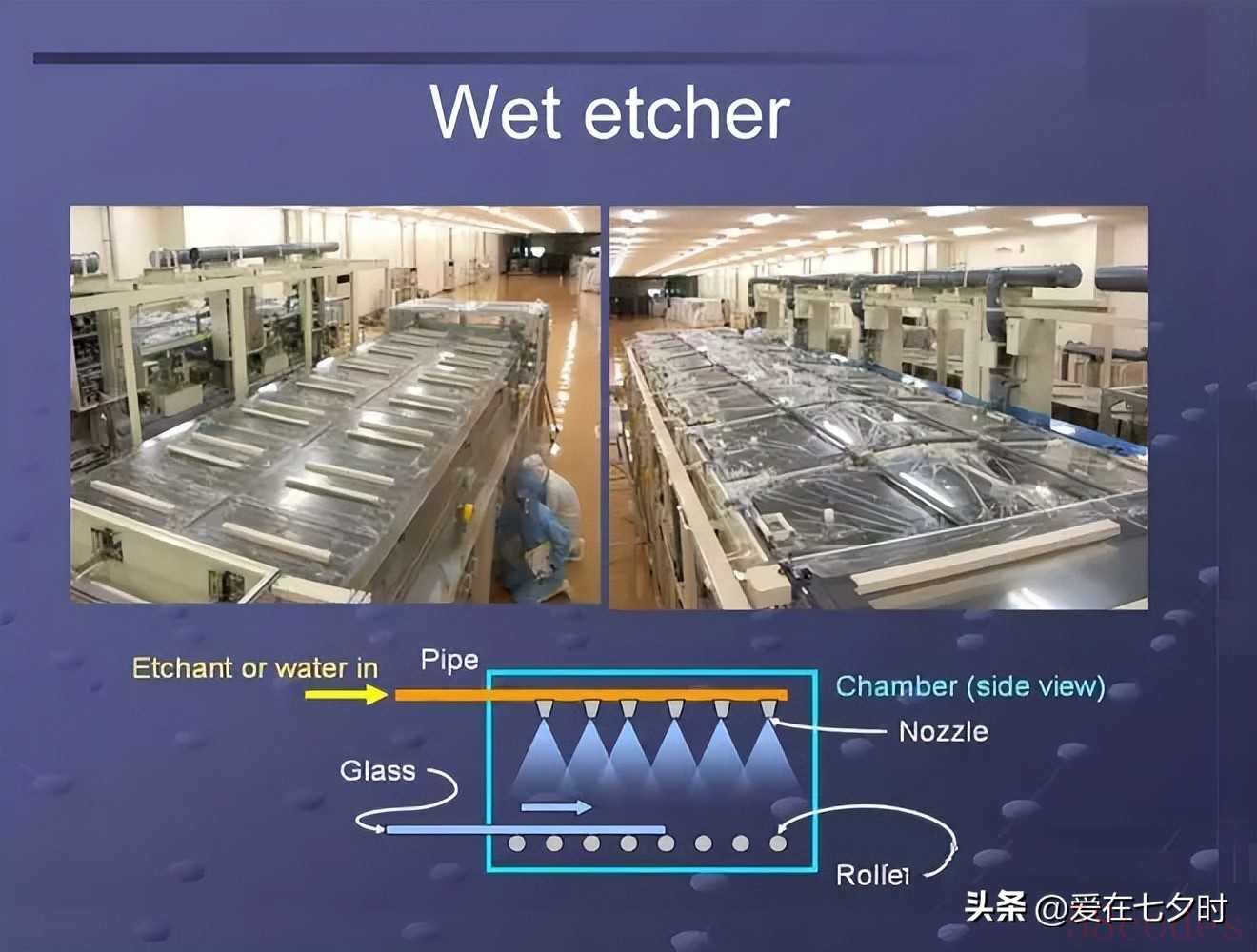

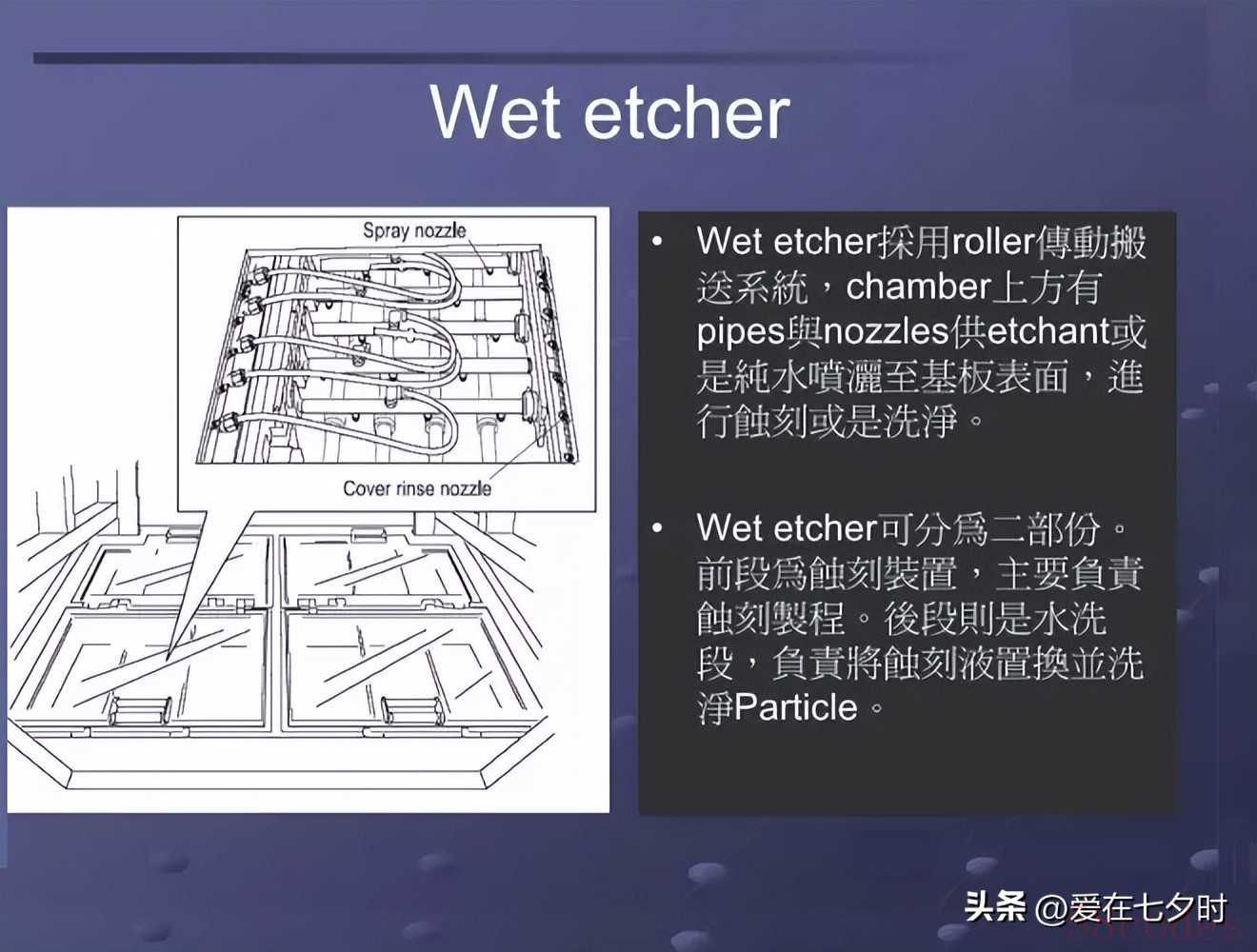

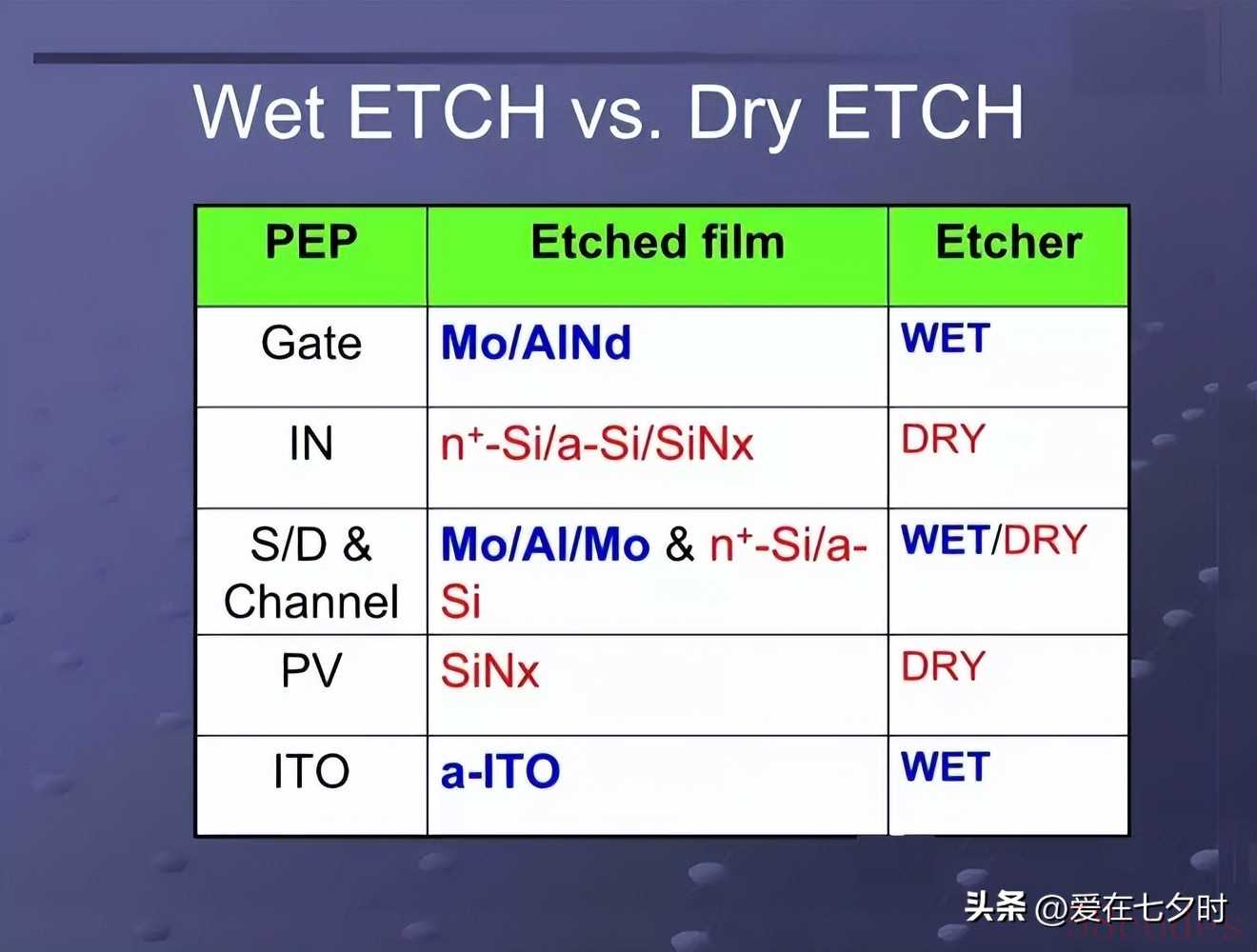

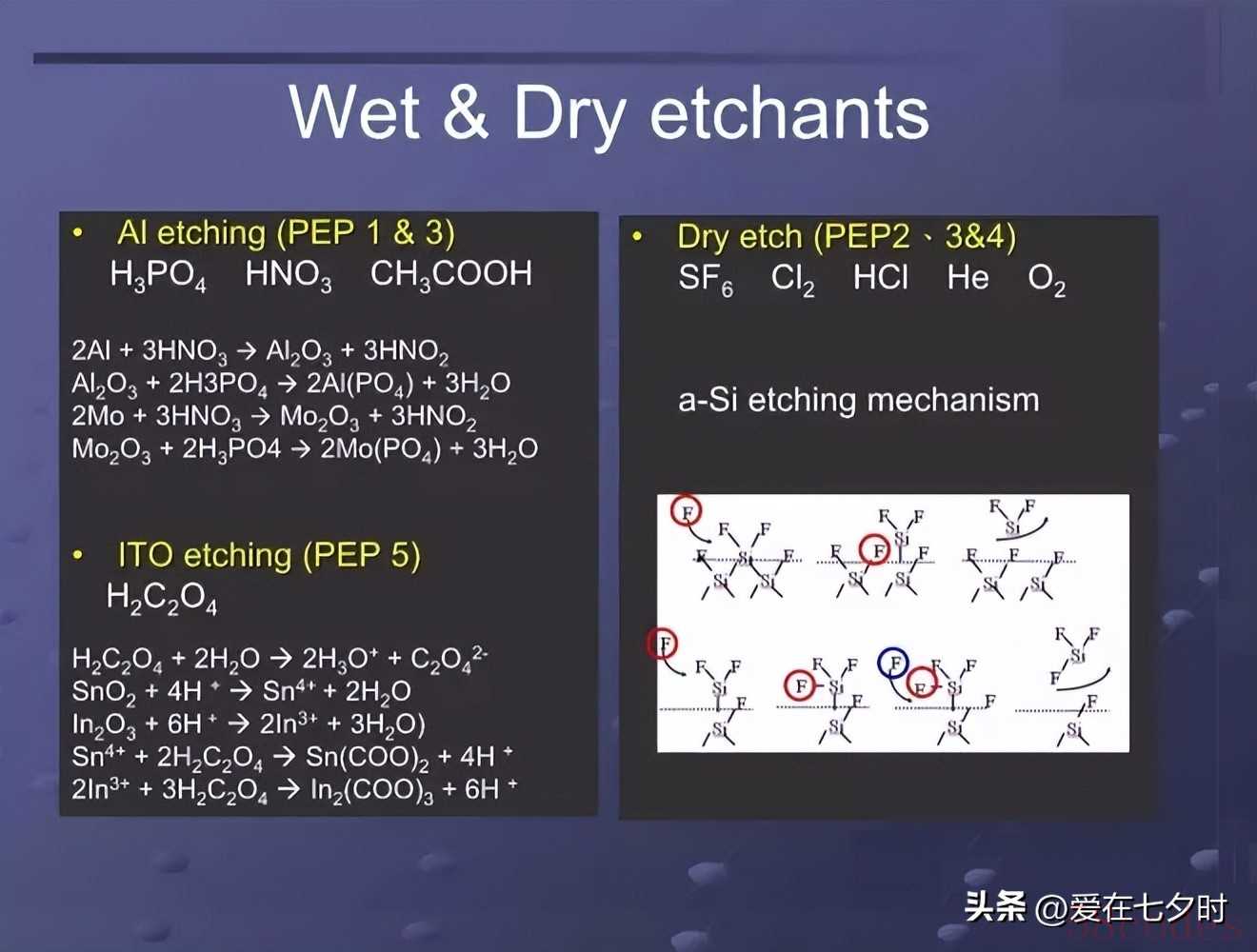

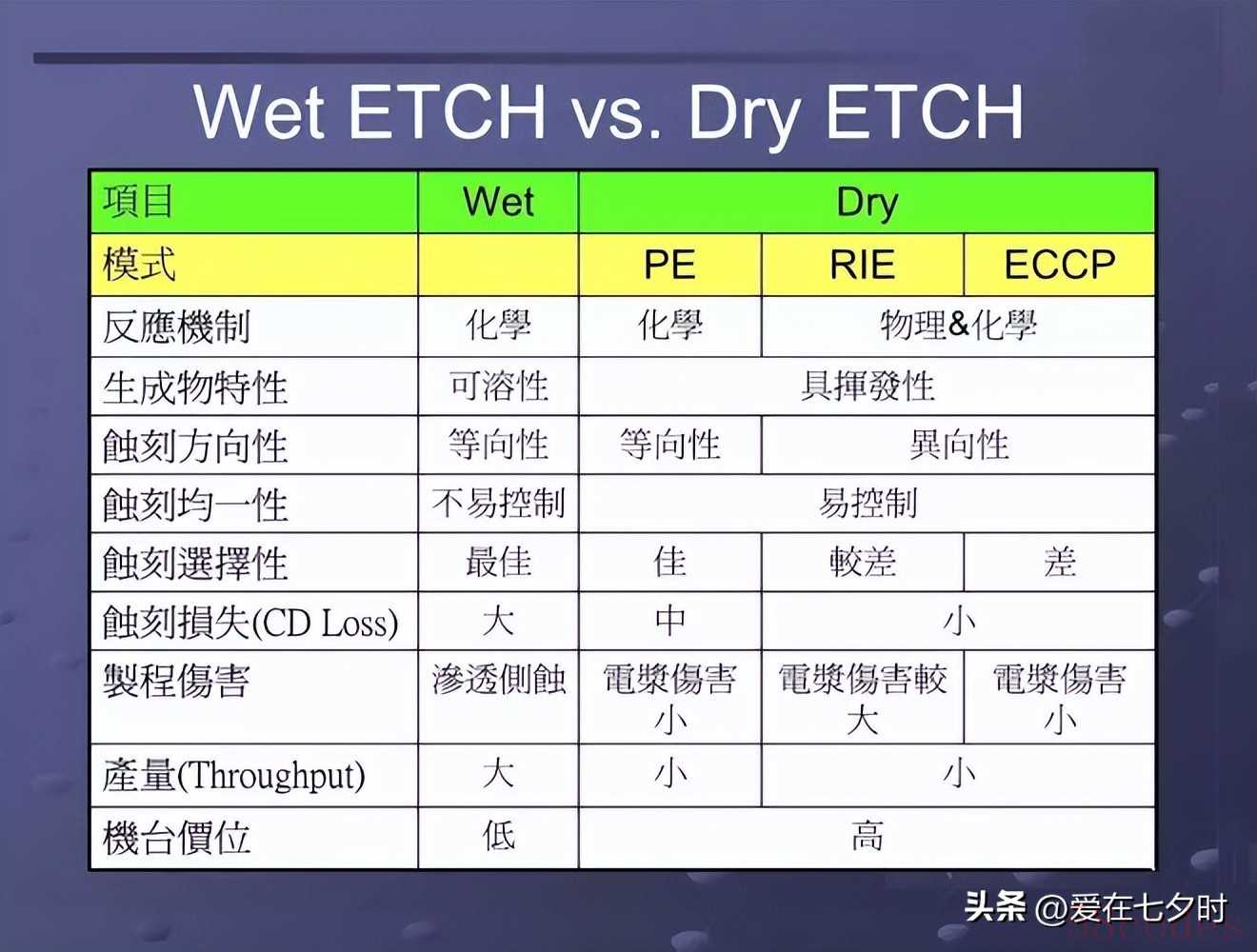

一、“刻蚀”工艺的介绍刻蚀,英文为Etch,它是半导体制造工艺,微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。是与光刻相联系的图形化(pattern)处理的一种主要工艺。所谓刻蚀,实际上狭义理解就是光刻腐蚀,先通过光刻将光刻胶进行光刻曝光处理,然后通过其它方式实现腐蚀处理掉所需除去的部分。刻蚀是用化学或物理方法有选择地从硅片表面去除不需要的材料的过程,其基本目标是在涂胶的硅片上正确地复制掩模图形。随着微制造工艺的发展,广义上来讲,刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称,成为微加工制造的一种普适叫法。 二、“刻蚀”工艺的分类刻蚀按大类来分,主要分为:湿法刻蚀和干法刻蚀两种,下面表格简单对两种刻蚀方法进行对比:

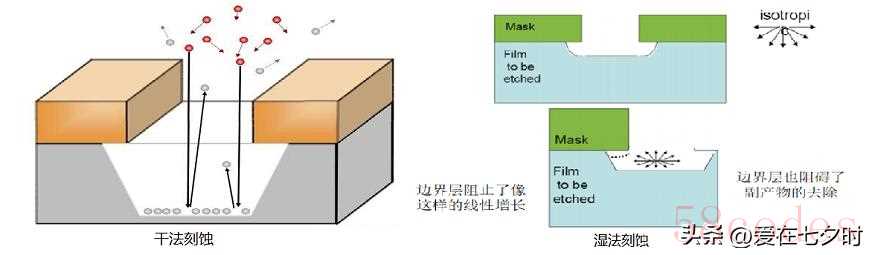

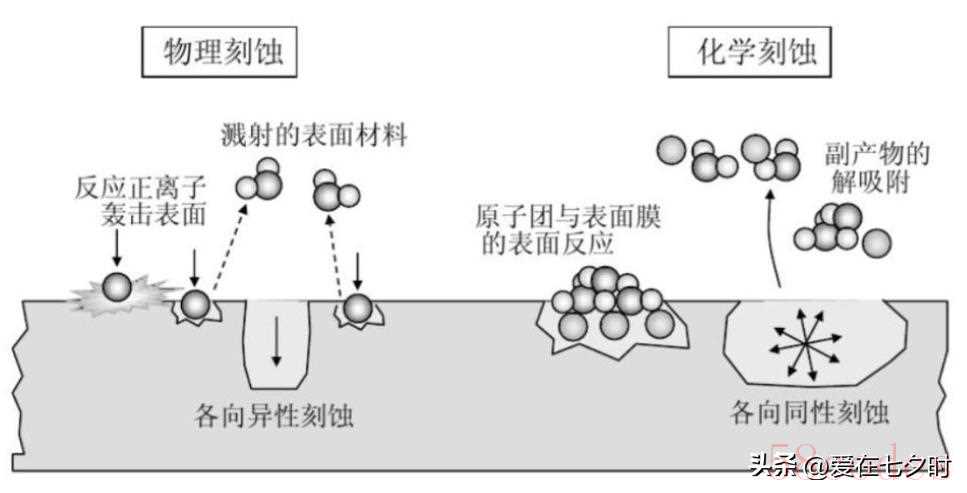

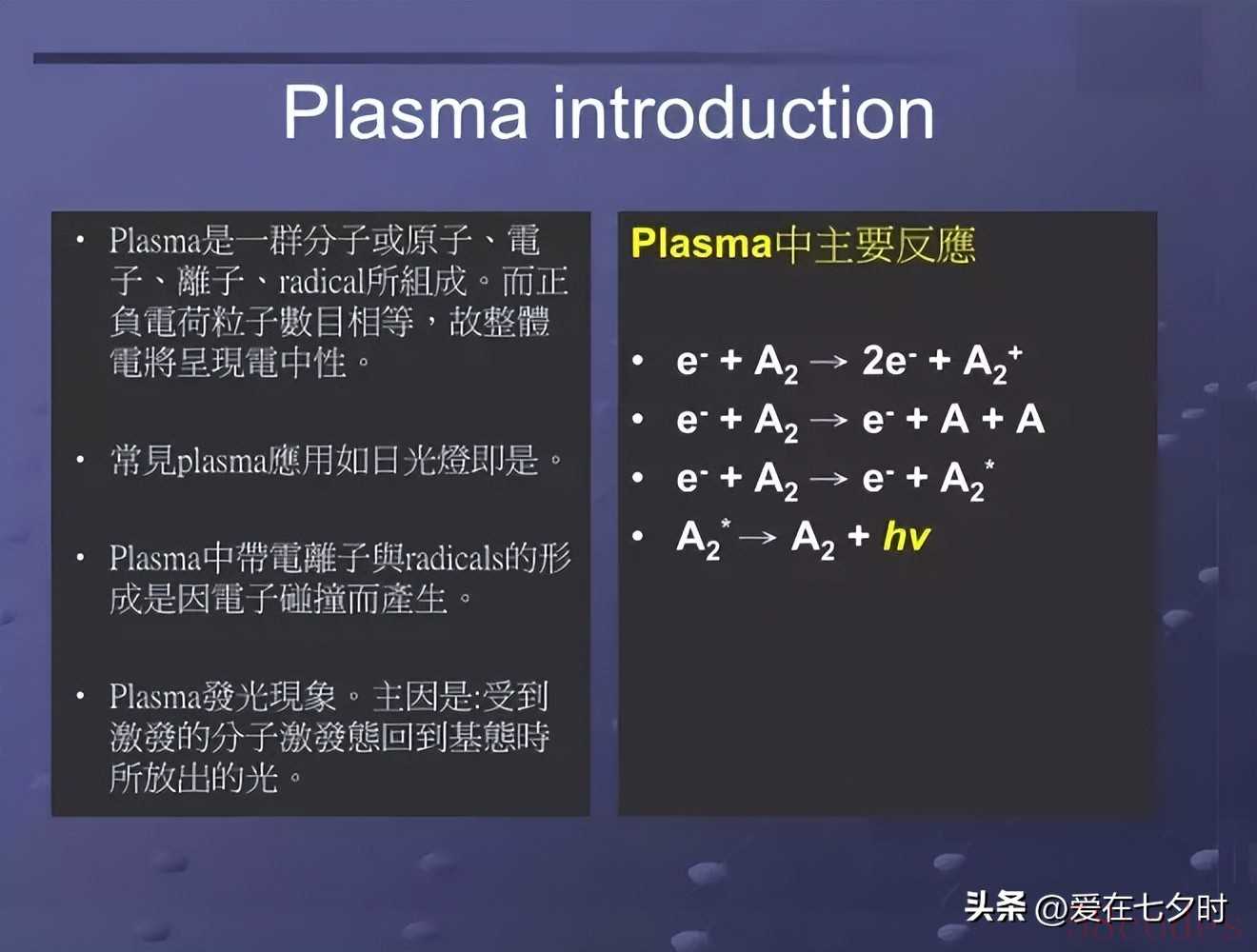

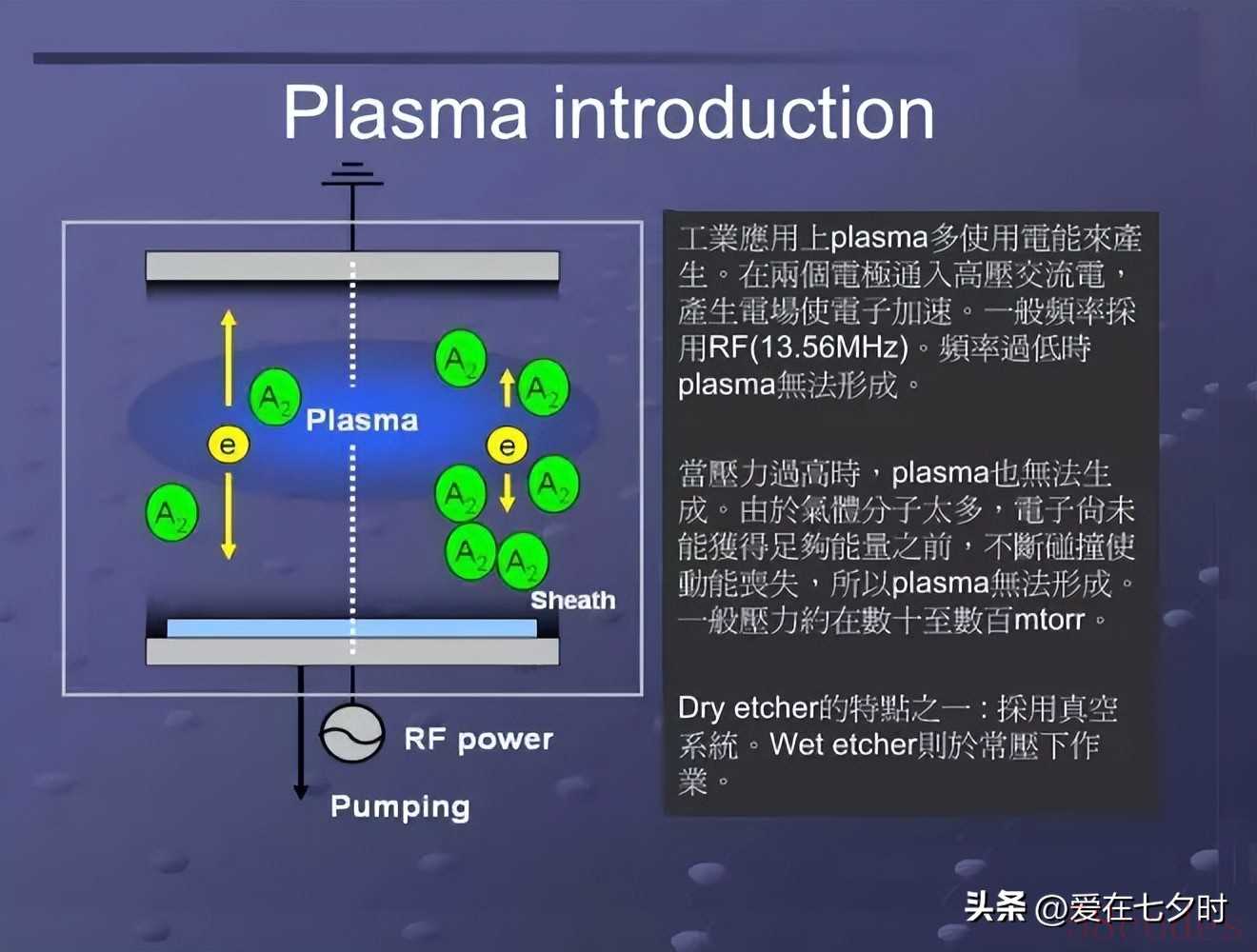

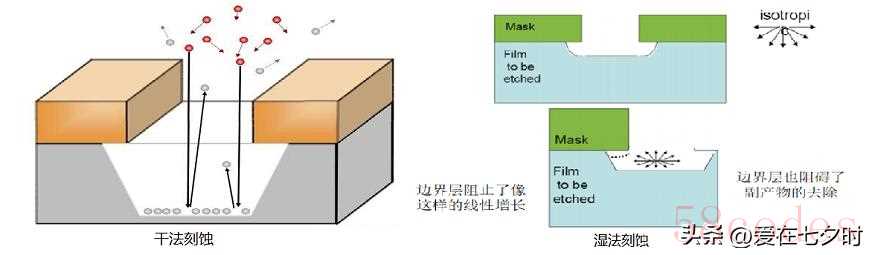

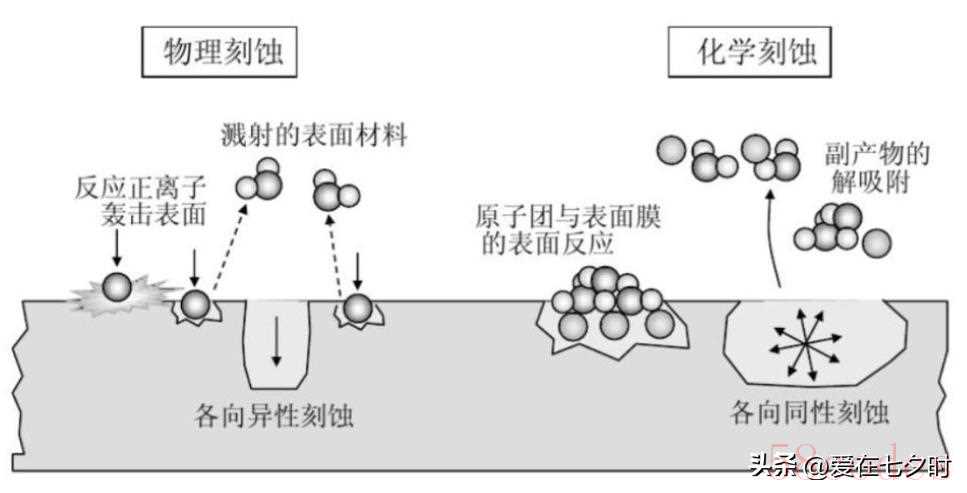

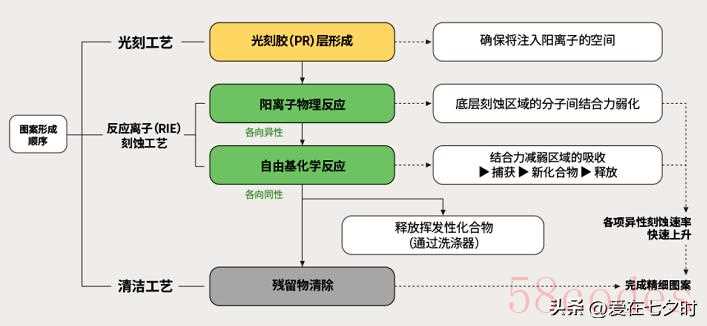

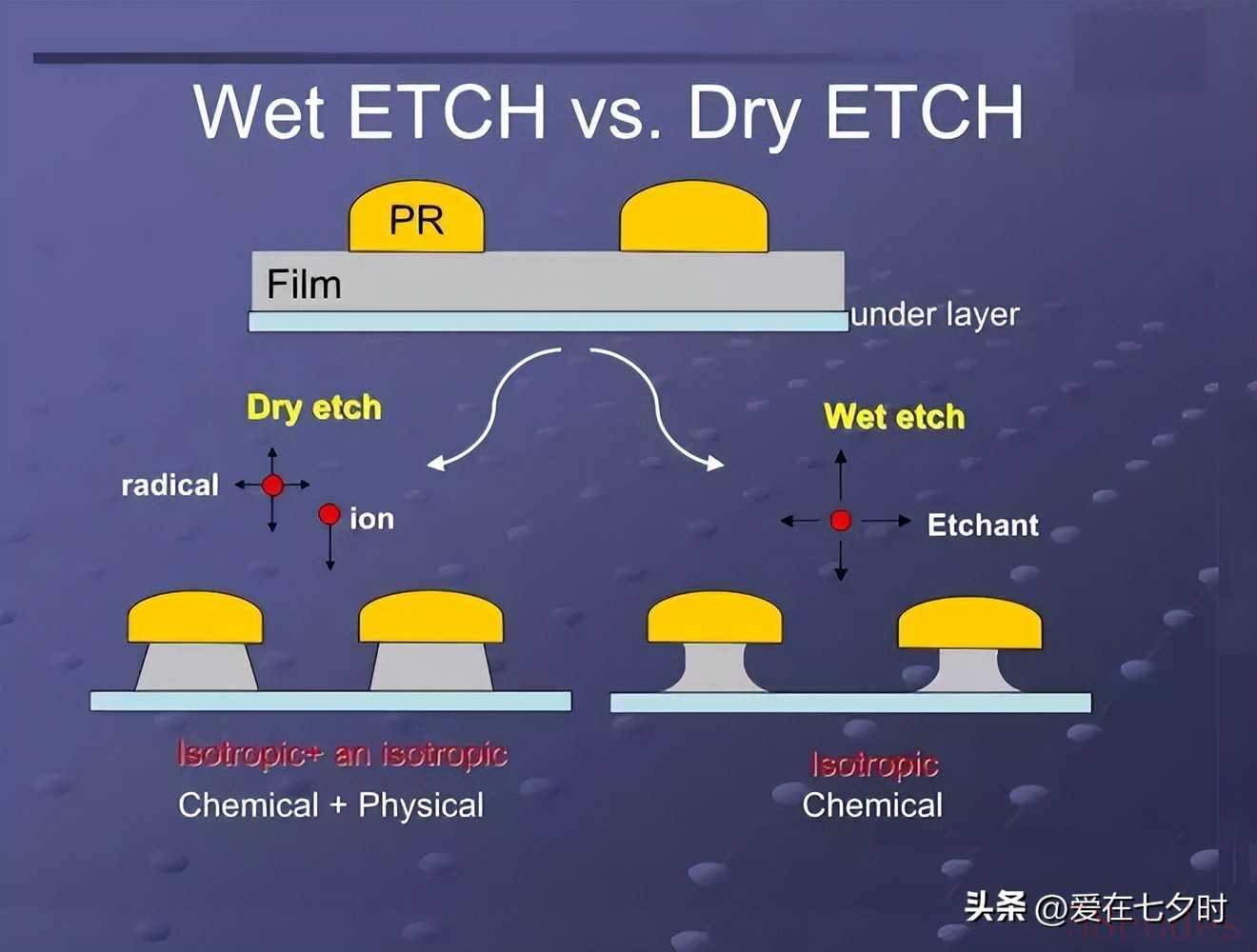

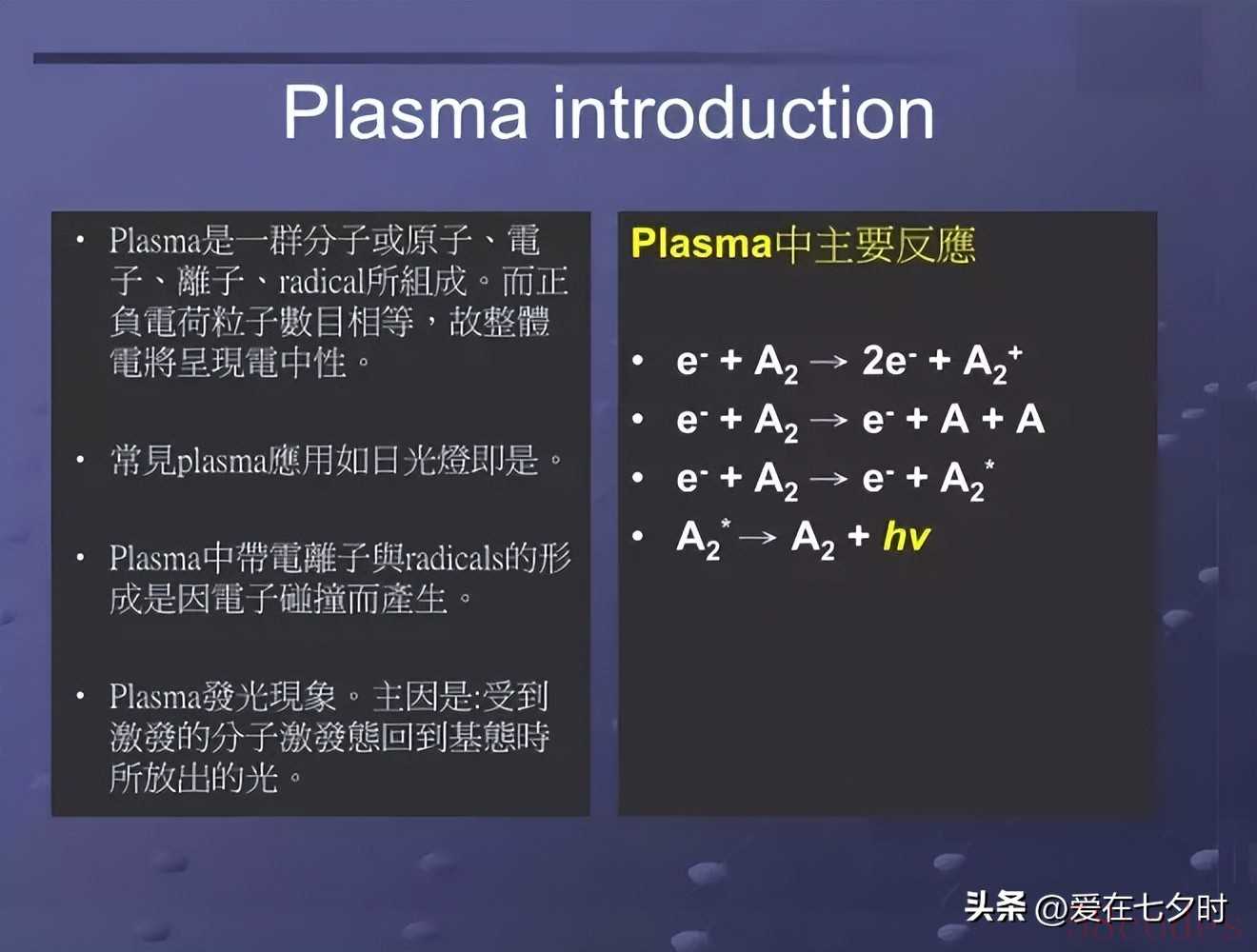

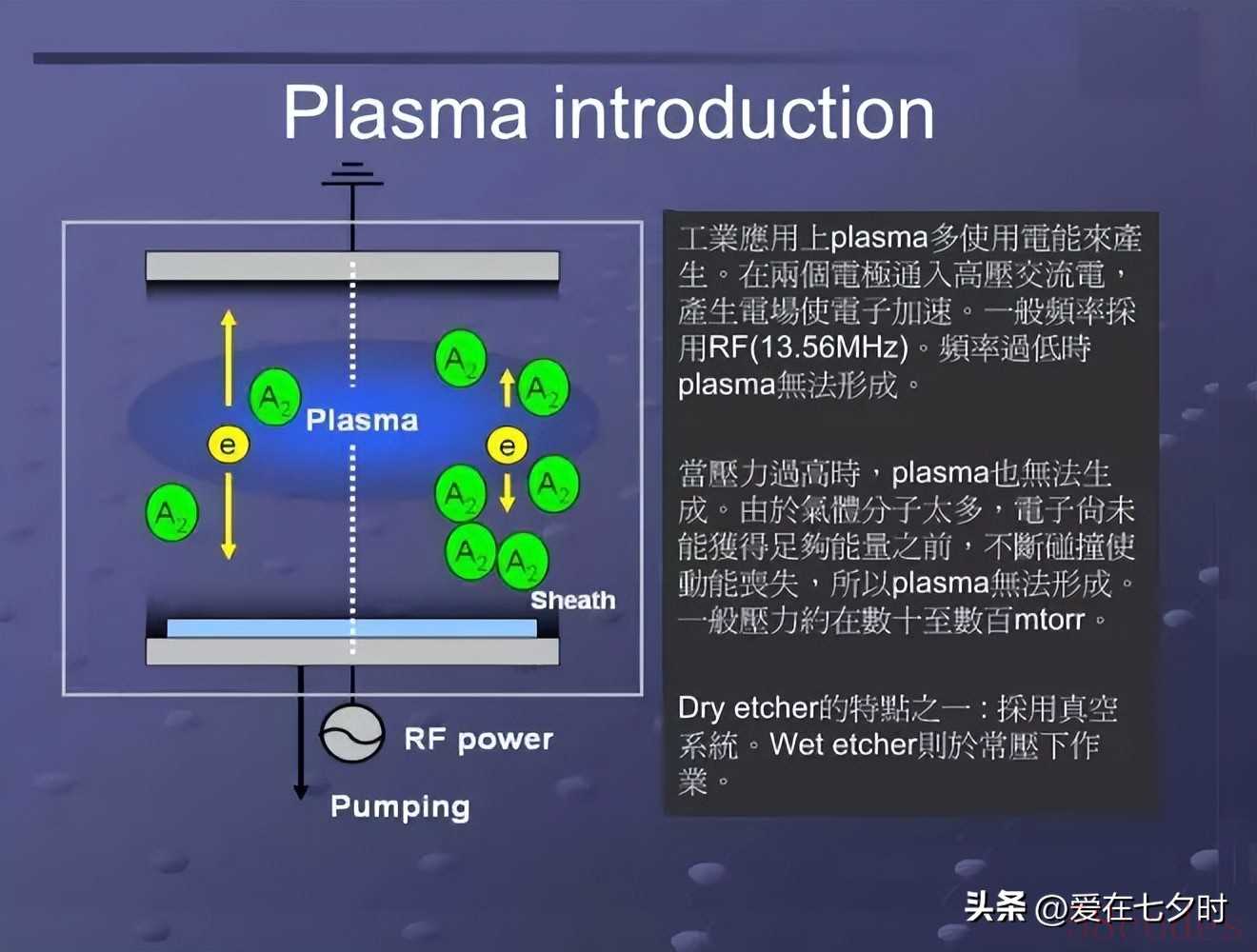

二、“刻蚀”工艺的分类刻蚀按大类来分,主要分为:湿法刻蚀和干法刻蚀两种,下面表格简单对两种刻蚀方法进行对比: 其中,在干法蚀刻中,气体受高频(主要为 13.56 MHz 或 2.45 GHz)激发。在 1 到 100 Pa 的压力下,其平均自由程为几毫米到几厘米。主要有三种类型的干法蚀刻:• 物理干法蚀刻:加速粒子对晶圆表面的物理磨损;• 化学干法蚀刻:气体与晶圆表面发生化学反应;• 化学物理干法蚀刻:具有化学特性的物理蚀刻工艺;

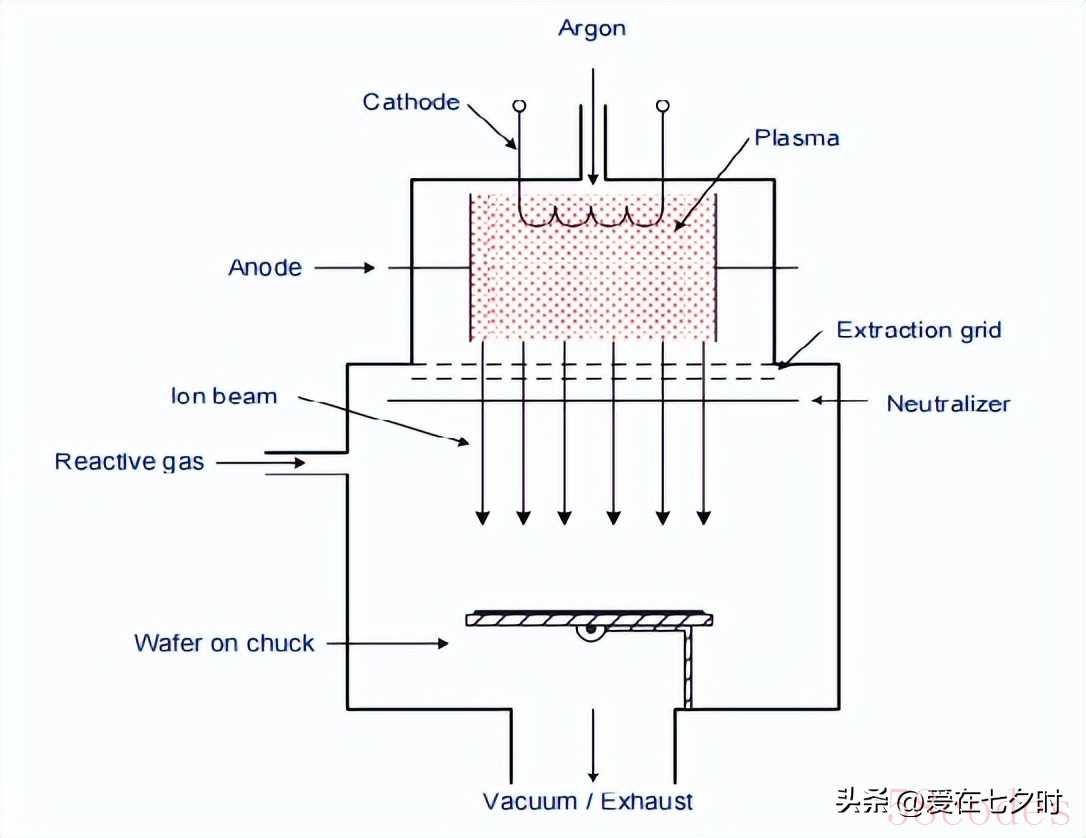

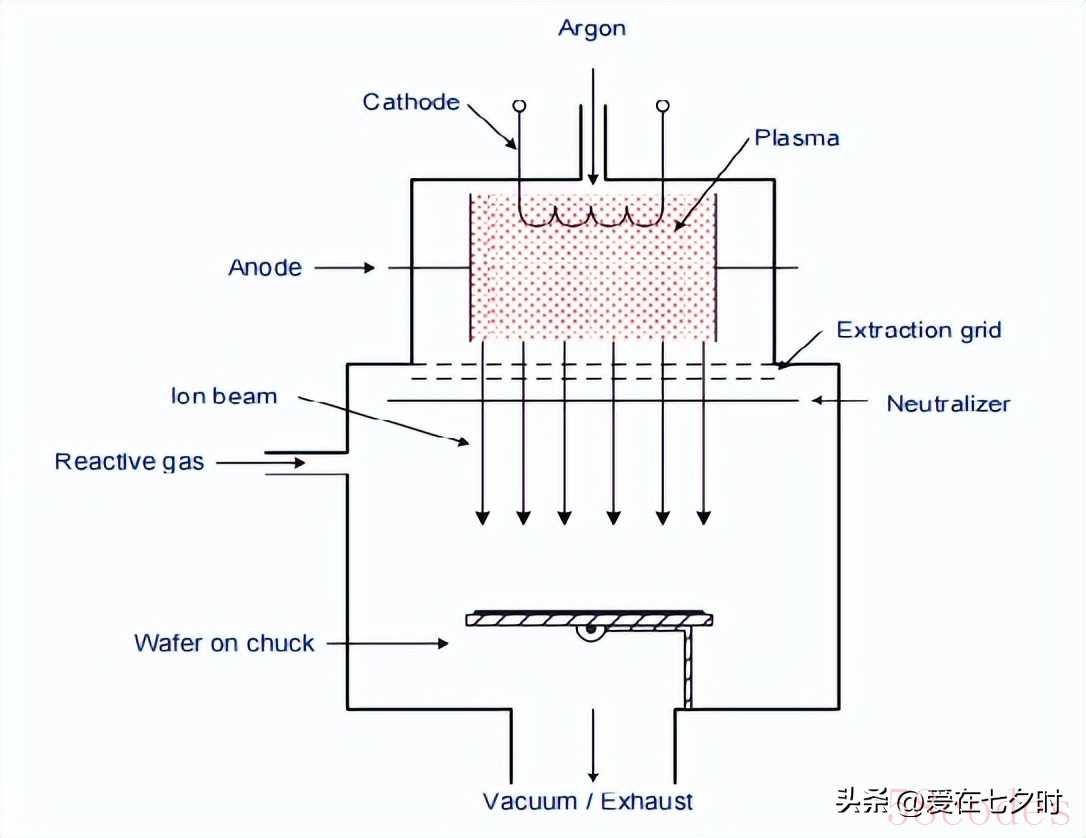

其中,在干法蚀刻中,气体受高频(主要为 13.56 MHz 或 2.45 GHz)激发。在 1 到 100 Pa 的压力下,其平均自由程为几毫米到几厘米。主要有三种类型的干法蚀刻:• 物理干法蚀刻:加速粒子对晶圆表面的物理磨损;• 化学干法蚀刻:气体与晶圆表面发生化学反应;• 化学物理干法蚀刻:具有化学特性的物理蚀刻工艺; 1、离子束蚀刻离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对各向异性的。选择性低,因为其对各个层没有差异。气体和被打磨出的材料被真空泵排出,但是,由于反应产物不是气态的,颗粒会沉积在晶片或室壁上。

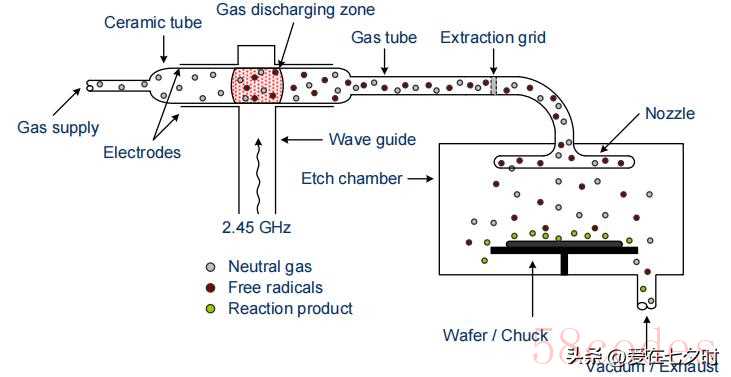

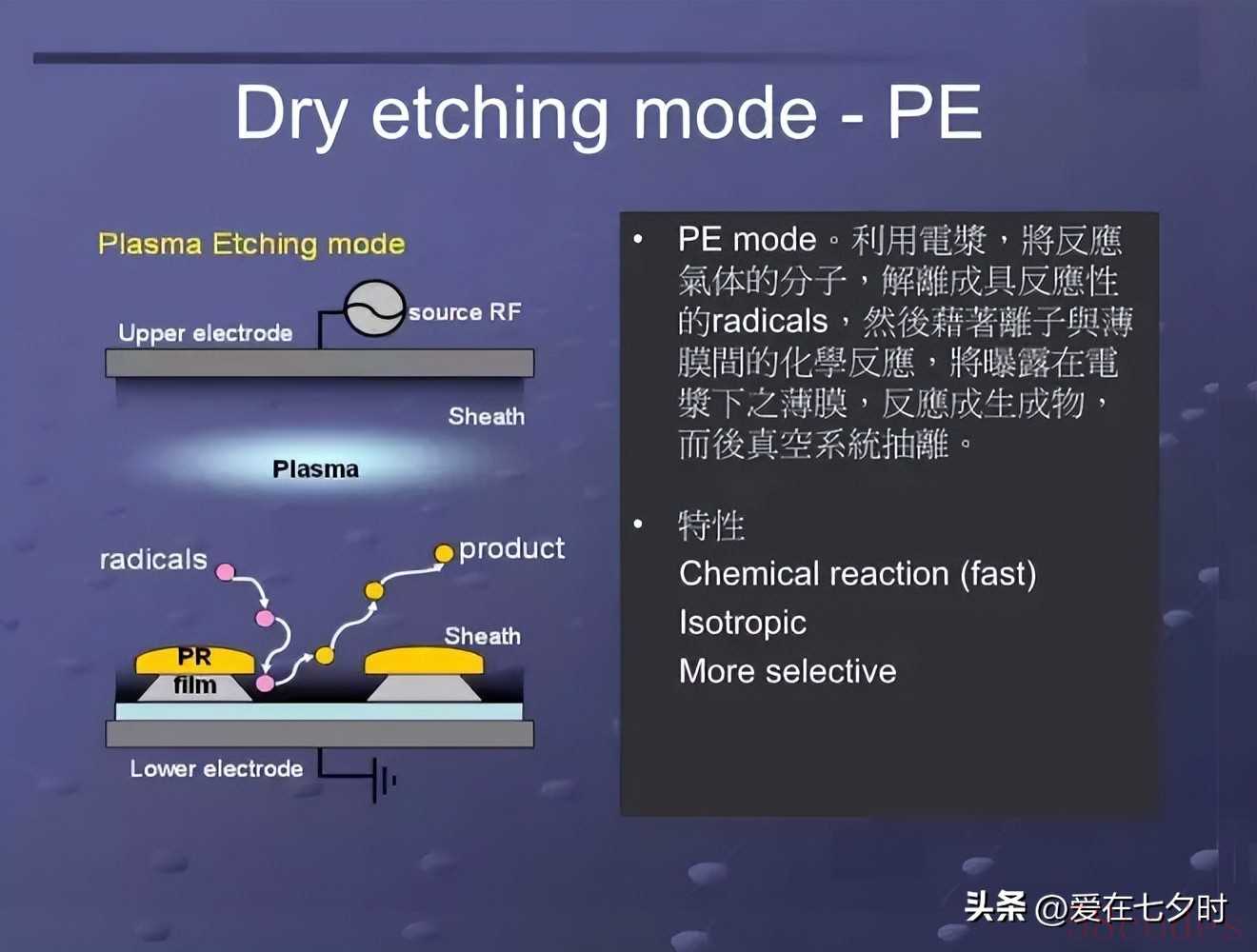

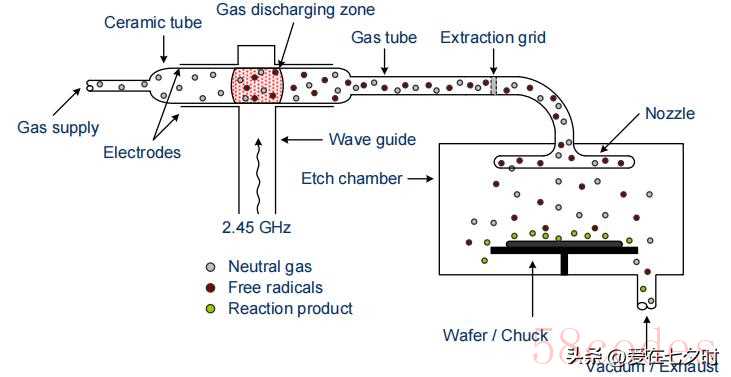

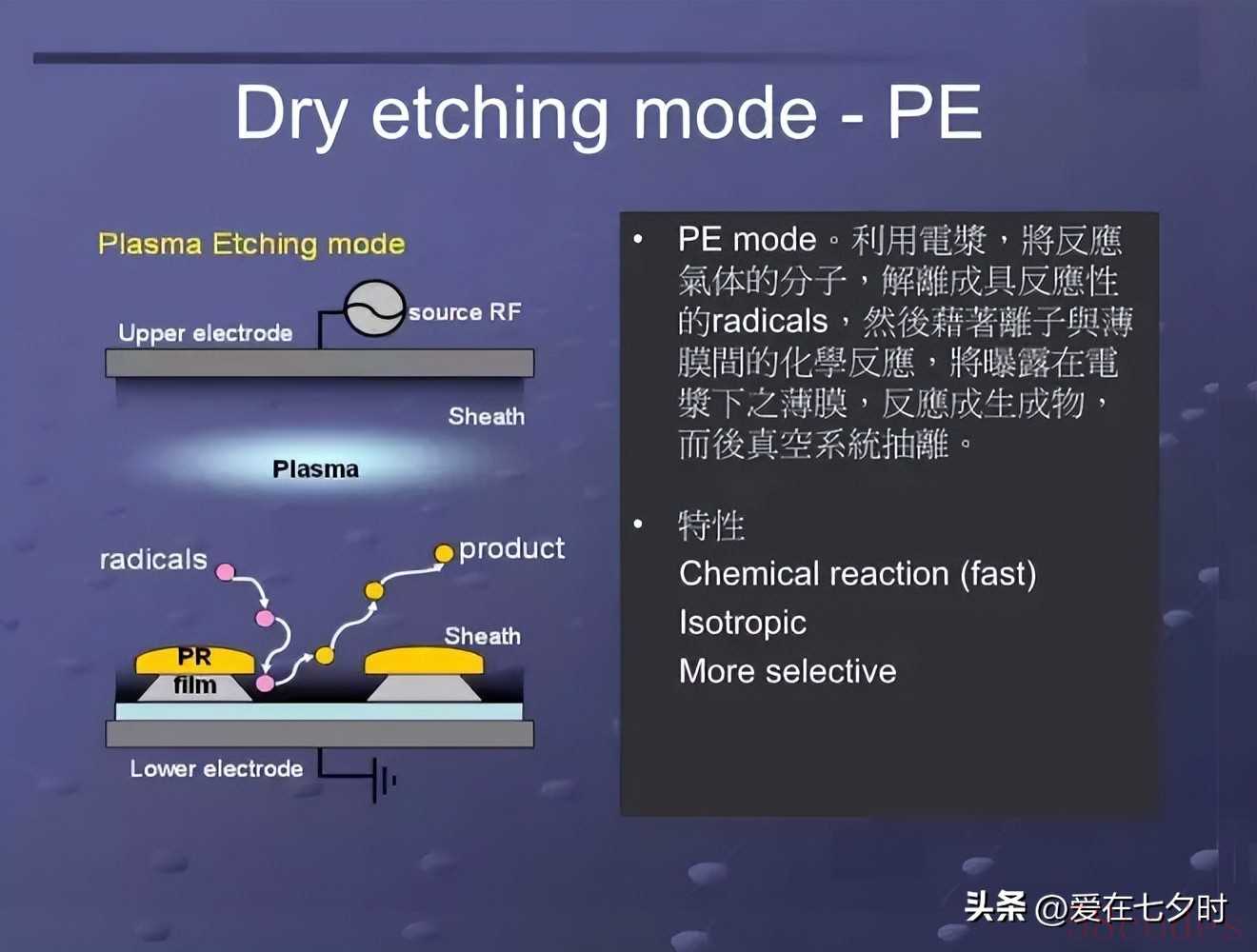

1、离子束蚀刻离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对各向异性的。选择性低,因为其对各个层没有差异。气体和被打磨出的材料被真空泵排出,但是,由于反应产物不是气态的,颗粒会沉积在晶片或室壁上。 为避免颗粒,将第二种气体引入腔室。该气体与氩离子发生反应并引起物理化学蚀刻过程。部分气体与表面反应,但也与打磨出的颗粒反应形成气态副产物。几乎所有材料都可以用这种方法蚀刻。由于垂直辐射,垂直壁上的磨损非常低(高各向异性)。然而,由于低选择性和低蚀刻速率,该工艺在当今的半导体制造中很少使用。2、等离子刻蚀等离子刻蚀(Plasma etch)是一种绝对化学刻蚀工艺(化学干法刻蚀,Chemical dry etch)。优点是晶圆表面不会被加速离子损坏。由于蚀刻气体的可移动颗粒,蚀刻轮廓是各向同性的,因此该方法用于去除整个膜层(如热氧化后的背面清洁)。一种用于等离子体蚀刻的反应器类型是下游反应器。从而通过碰撞电离在2.45GHz的高频下点燃等离子体,碰撞电离的位置与晶片分离。

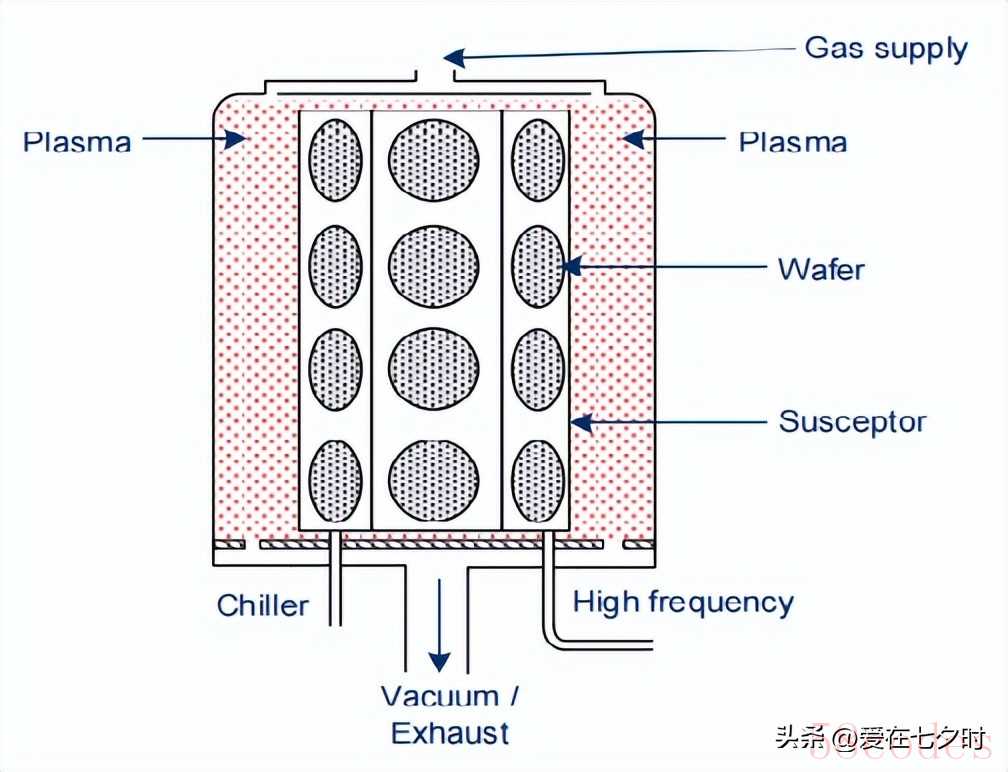

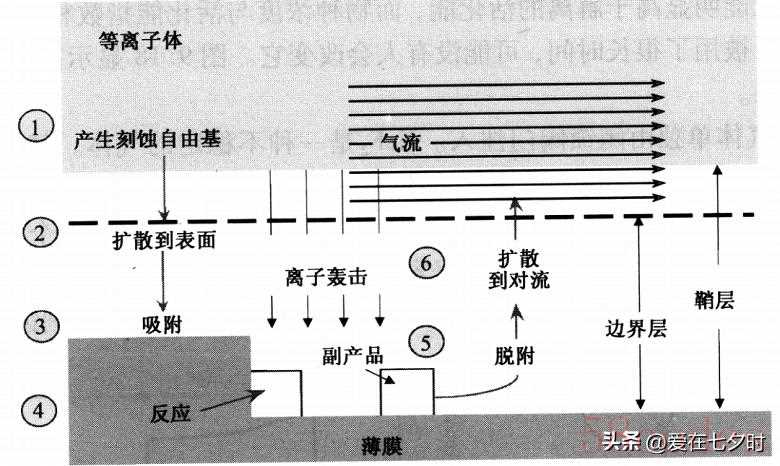

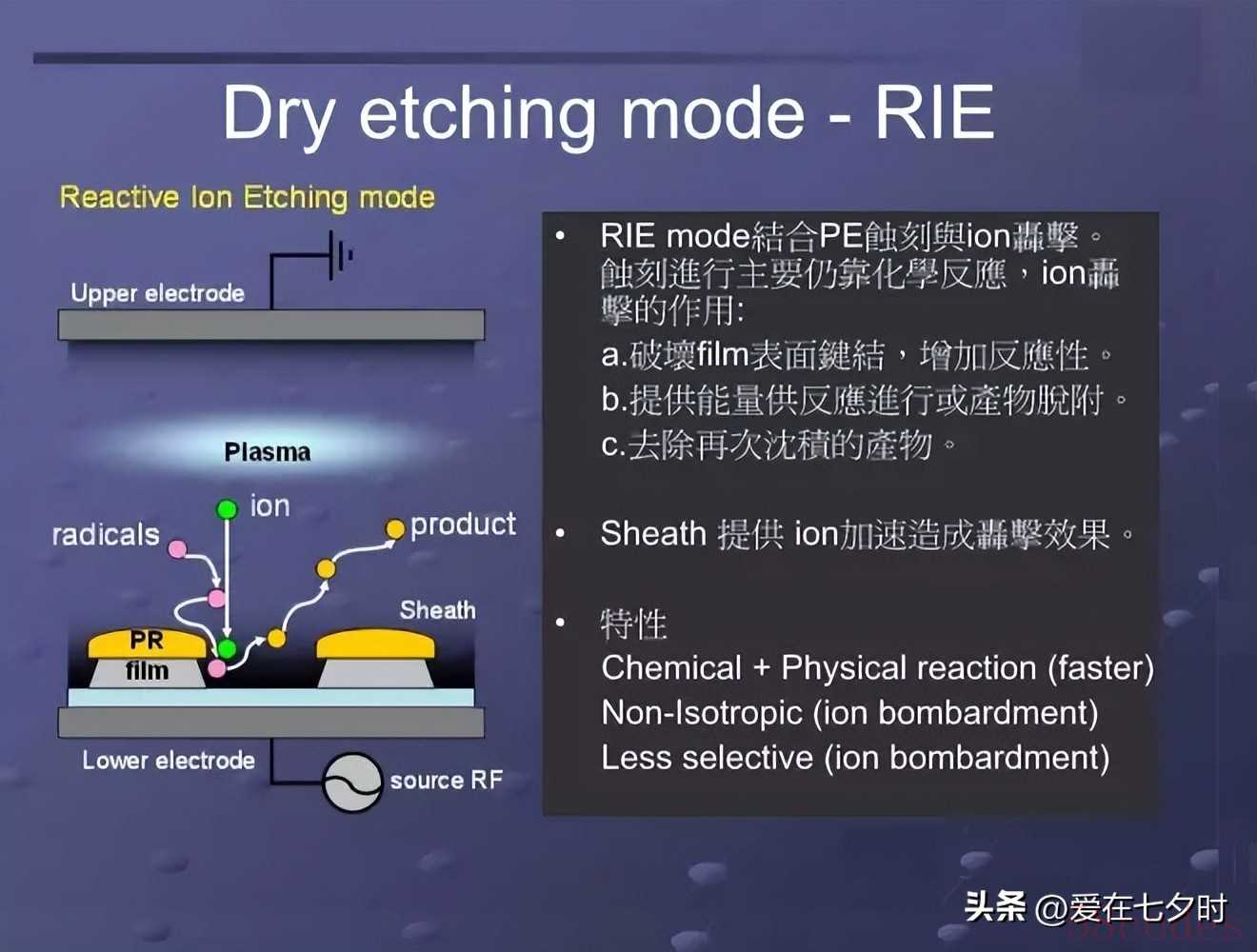

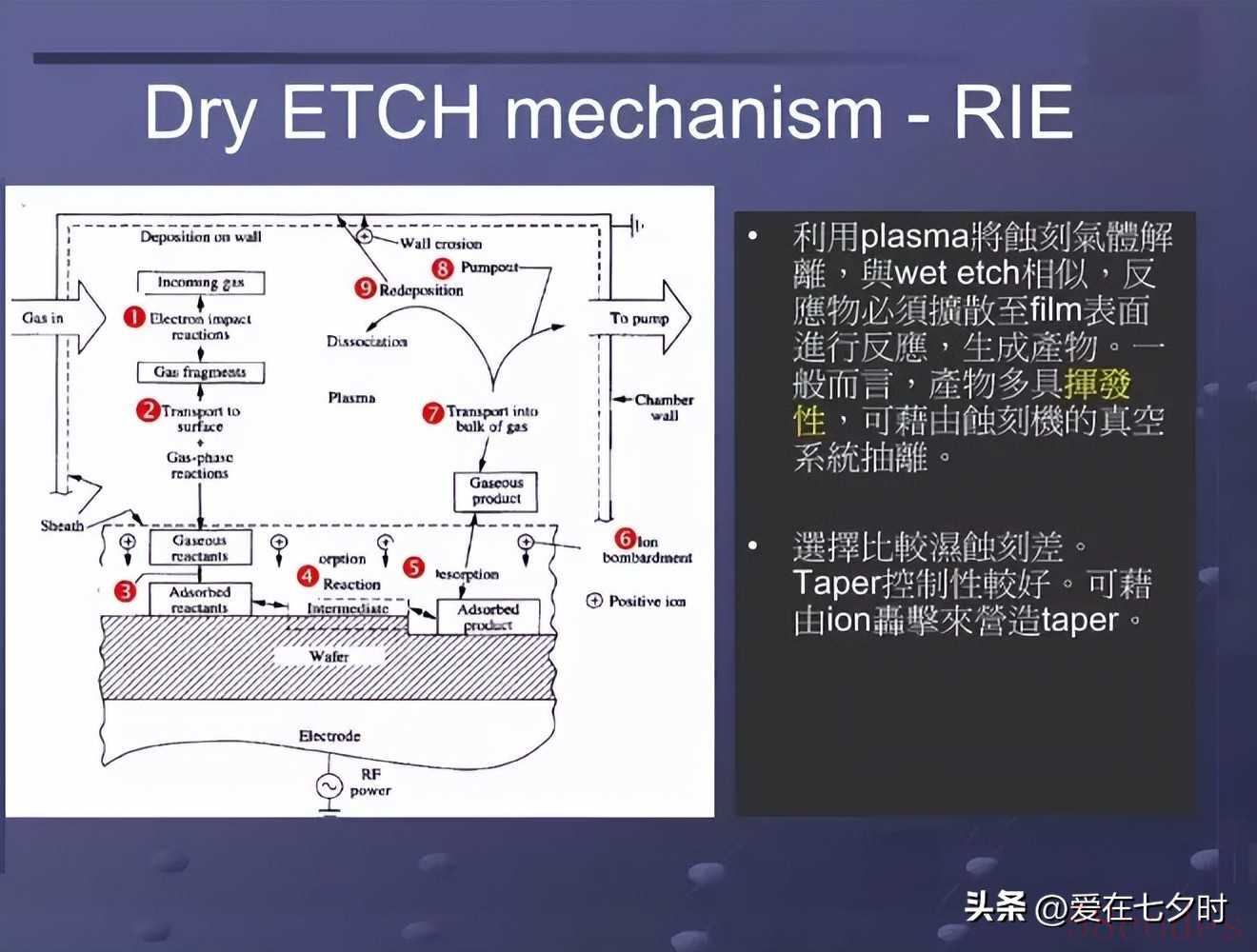

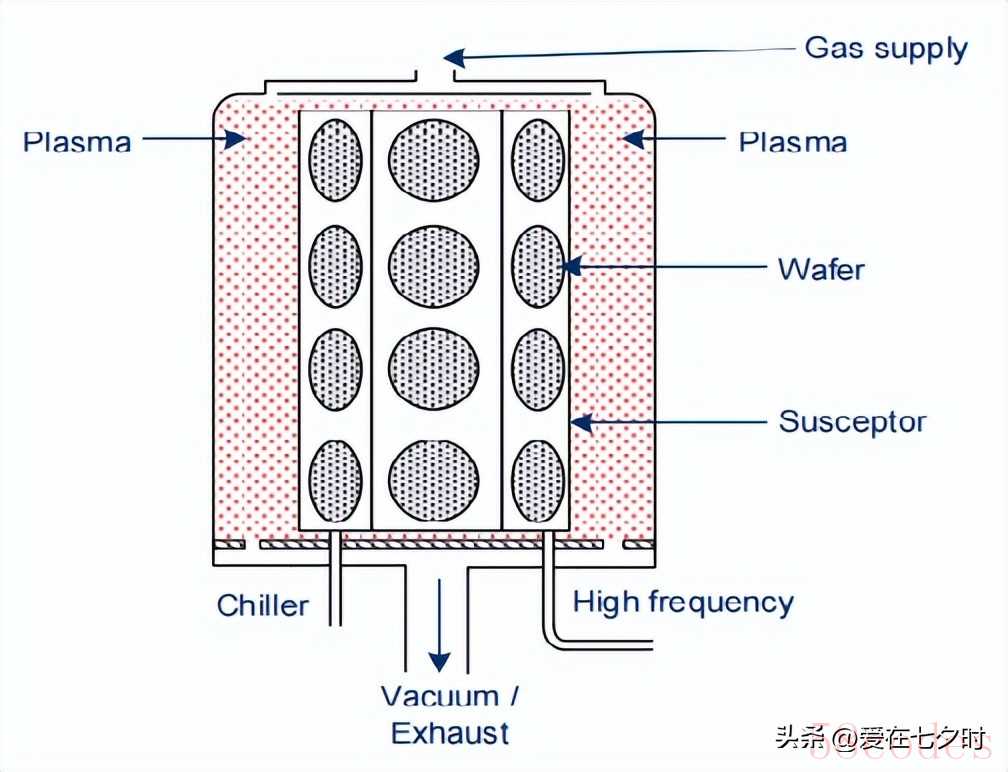

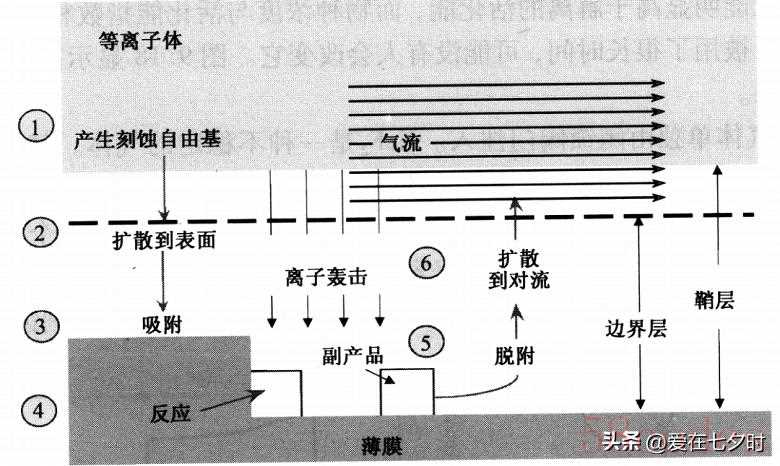

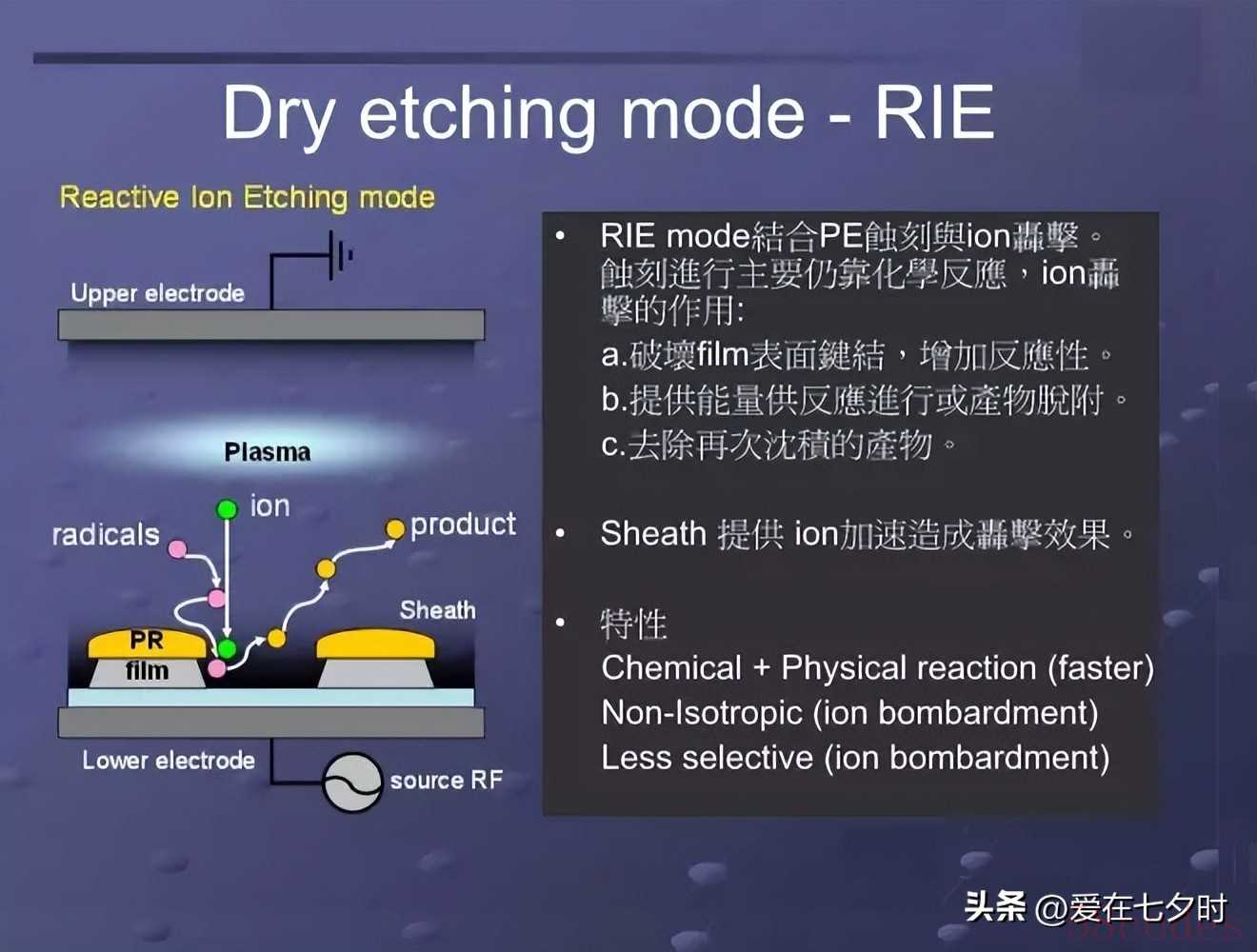

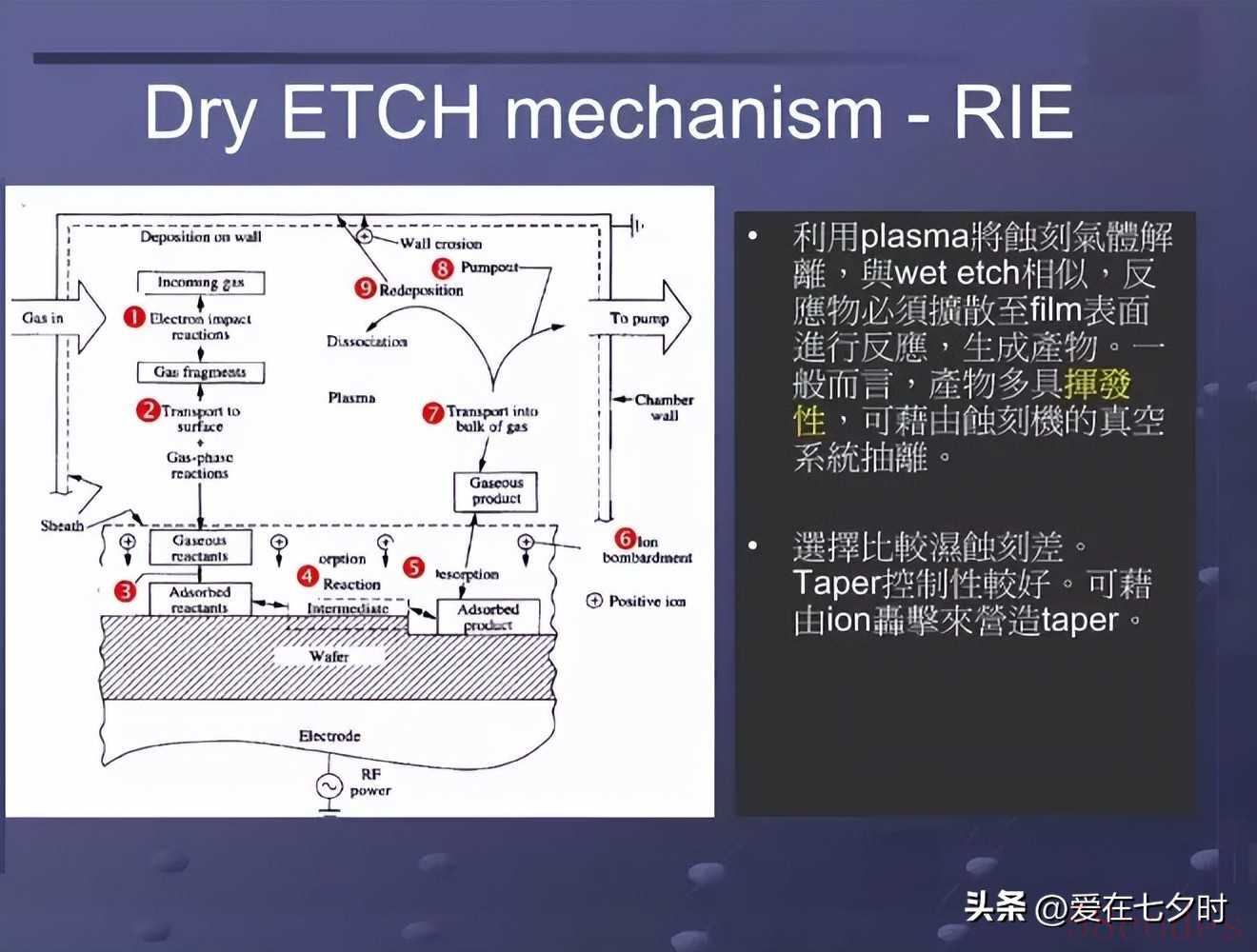

为避免颗粒,将第二种气体引入腔室。该气体与氩离子发生反应并引起物理化学蚀刻过程。部分气体与表面反应,但也与打磨出的颗粒反应形成气态副产物。几乎所有材料都可以用这种方法蚀刻。由于垂直辐射,垂直壁上的磨损非常低(高各向异性)。然而,由于低选择性和低蚀刻速率,该工艺在当今的半导体制造中很少使用。2、等离子刻蚀等离子刻蚀(Plasma etch)是一种绝对化学刻蚀工艺(化学干法刻蚀,Chemical dry etch)。优点是晶圆表面不会被加速离子损坏。由于蚀刻气体的可移动颗粒,蚀刻轮廓是各向同性的,因此该方法用于去除整个膜层(如热氧化后的背面清洁)。一种用于等离子体蚀刻的反应器类型是下游反应器。从而通过碰撞电离在2.45GHz的高频下点燃等离子体,碰撞电离的位置与晶片分离。 在气体放电区域,由于冲击存在各种颗粒,其中有自由基。自由基是具有不饱和电子的中性原子或分子,因此非常活泼。作为中性气体,例如四氟甲烷CF4被引入气体放电区并分离成CF2和氟分子F2。类似地,氟可以通过添加氧气 O2 从 CF4 中分离出来:2 CF4 + O2 --->2 COF2 + 2 F2氟分子可以通过气体放电区的能量分裂成两个单独的氟原子:每个氟原子都是一个氟自由基,因为每个原子都有七个价电子,并希望实现惰性气体构型。除了中性自由基之外,还有几个部分带电的粒子(CF+4、CF+3、CF+2、...)。然后,所有粒子、自由基等都通过陶瓷管进入蚀刻室。带电粒子可以通过提取光栅从蚀刻室中阻挡或者在它们形成中性分子的途中重新组合。氟自由基也有部分重组,但足以到达蚀刻室,在晶圆表面发生反应并引起化学磨损。其他中性粒子不是蚀刻过程的一部分,并且与反应产物一样被耗尽。可在等离子蚀刻中蚀刻的薄膜示例: • 硅: Si + 4F---> SiF4 • 二氧化硅: SiO2 + 4F---> SiF4 + O2 • 氮化硅: Si3N4 + 12F---> 3SiF4 + 2N23.反应离子蚀刻蚀刻特性: 选择性、蚀刻轮廓、蚀刻速率、均匀性、可重复性 - 均可以在反应离子蚀刻 (Reactive ion etch) 中非常精确地控制。各向同性蚀刻轮廓以及各向异性是可能的。因此,RIE 工艺是一种化学物理蚀刻工艺,是半导体制造中用于构造各种薄膜的最重要工艺。 在工艺室内,晶圆放置在高频电极(HF电极)上。通过碰撞电离产生等离子体,其中出现自由电子和带正电的离子。如果 HF 电极处于正电压,则自由电子会在其上积聚,并且由于它们的电子亲和力而无法再次离开电极。因此,电极充电至 -1000 V(偏置电压)。不能跟随快速交变场的慢离子向带负电的电极移动。

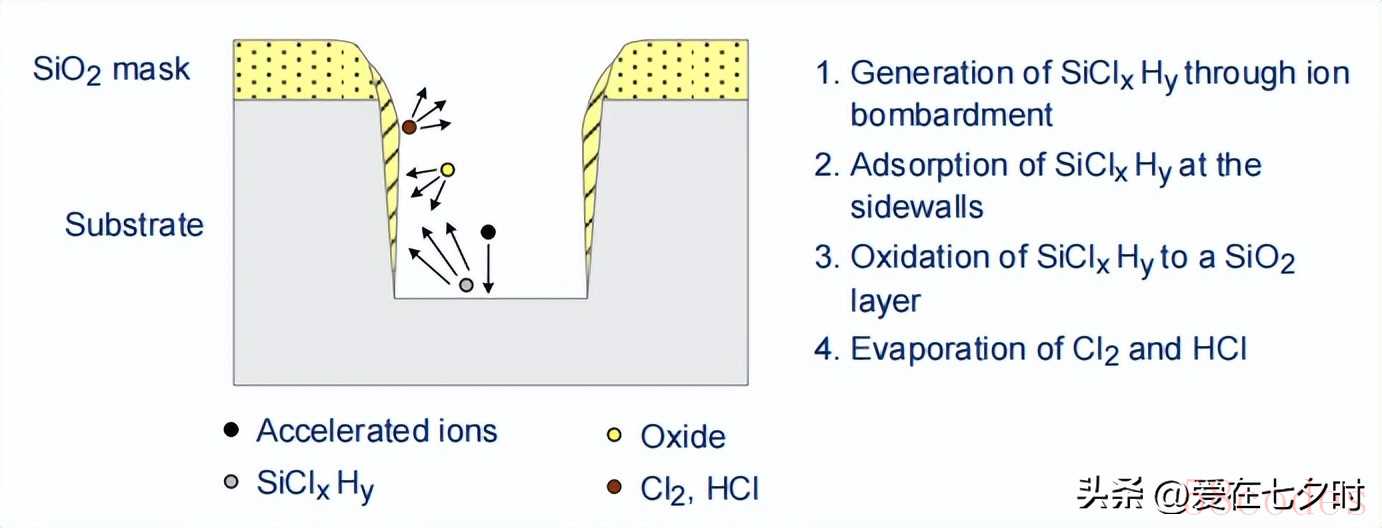

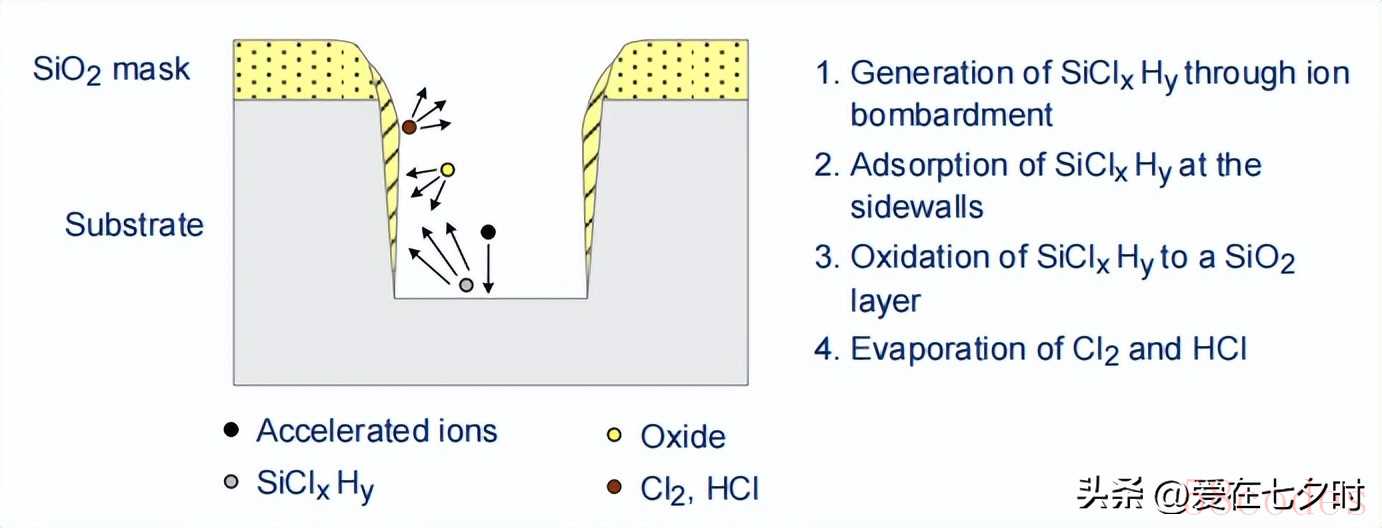

在气体放电区域,由于冲击存在各种颗粒,其中有自由基。自由基是具有不饱和电子的中性原子或分子,因此非常活泼。作为中性气体,例如四氟甲烷CF4被引入气体放电区并分离成CF2和氟分子F2。类似地,氟可以通过添加氧气 O2 从 CF4 中分离出来:2 CF4 + O2 --->2 COF2 + 2 F2氟分子可以通过气体放电区的能量分裂成两个单独的氟原子:每个氟原子都是一个氟自由基,因为每个原子都有七个价电子,并希望实现惰性气体构型。除了中性自由基之外,还有几个部分带电的粒子(CF+4、CF+3、CF+2、...)。然后,所有粒子、自由基等都通过陶瓷管进入蚀刻室。带电粒子可以通过提取光栅从蚀刻室中阻挡或者在它们形成中性分子的途中重新组合。氟自由基也有部分重组,但足以到达蚀刻室,在晶圆表面发生反应并引起化学磨损。其他中性粒子不是蚀刻过程的一部分,并且与反应产物一样被耗尽。可在等离子蚀刻中蚀刻的薄膜示例: • 硅: Si + 4F---> SiF4 • 二氧化硅: SiO2 + 4F---> SiF4 + O2 • 氮化硅: Si3N4 + 12F---> 3SiF4 + 2N23.反应离子蚀刻蚀刻特性: 选择性、蚀刻轮廓、蚀刻速率、均匀性、可重复性 - 均可以在反应离子蚀刻 (Reactive ion etch) 中非常精确地控制。各向同性蚀刻轮廓以及各向异性是可能的。因此,RIE 工艺是一种化学物理蚀刻工艺,是半导体制造中用于构造各种薄膜的最重要工艺。 在工艺室内,晶圆放置在高频电极(HF电极)上。通过碰撞电离产生等离子体,其中出现自由电子和带正电的离子。如果 HF 电极处于正电压,则自由电子会在其上积聚,并且由于它们的电子亲和力而无法再次离开电极。因此,电极充电至 -1000 V(偏置电压)。不能跟随快速交变场的慢离子向带负电的电极移动。 如果离子的平均自由程高,则粒子以几乎垂直的方向撞击晶片表面。因此,材料被加速离子(物理蚀刻)从表面击出,此外,一些粒子与表面发生化学反应。横向侧壁不受影响,因此没有磨损并且蚀刻轮廓保持各向异性。选择性不是太小,但是,由于物理蚀刻进程,它也不是太大。此外,晶圆表面会被加速离子损坏,必须通过热退火进行固化。 蚀刻工艺的化学部分是通过自由基与表面以及物理铣削材料的反应来完成的,这样它就不会像离子束蚀刻那样重新沉积到晶圆或腔室壁上。通过增加蚀刻室中的压力,颗粒的平均自由程减少。因此会有更多的碰撞,因此粒子会朝着不同的方向前进。这导致较少的定向蚀刻,蚀刻过程获得更多的化学特性。选择性增加,蚀刻轮廓更加各向同性。通过在硅蚀刻期间侧壁的钝化,实现了各向异性的蚀刻轮廓。因此,蚀刻室内的氧气与磨出的硅反应形成二氧化硅,二氧化硅沉积垂直侧壁。由于离子轰击,水平区域上的氧化膜被去除,使得横向的蚀刻进程继续进行。

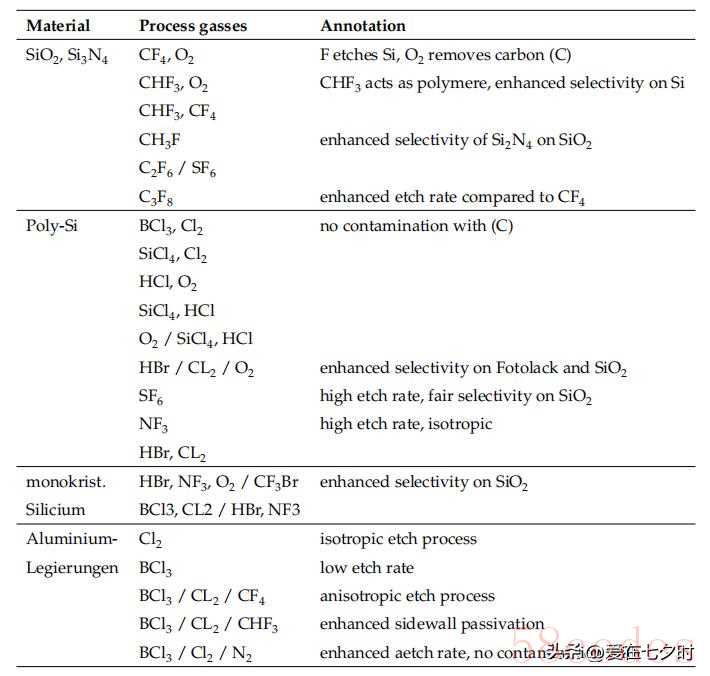

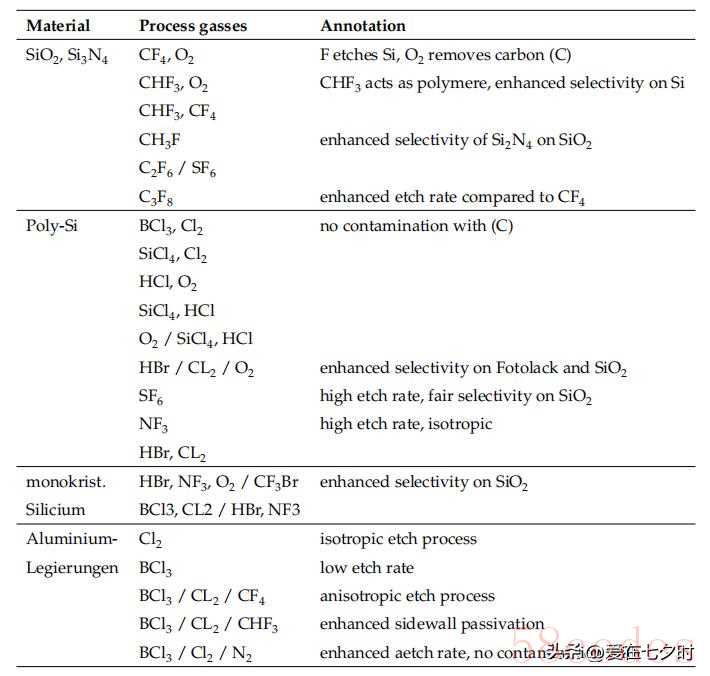

如果离子的平均自由程高,则粒子以几乎垂直的方向撞击晶片表面。因此,材料被加速离子(物理蚀刻)从表面击出,此外,一些粒子与表面发生化学反应。横向侧壁不受影响,因此没有磨损并且蚀刻轮廓保持各向异性。选择性不是太小,但是,由于物理蚀刻进程,它也不是太大。此外,晶圆表面会被加速离子损坏,必须通过热退火进行固化。 蚀刻工艺的化学部分是通过自由基与表面以及物理铣削材料的反应来完成的,这样它就不会像离子束蚀刻那样重新沉积到晶圆或腔室壁上。通过增加蚀刻室中的压力,颗粒的平均自由程减少。因此会有更多的碰撞,因此粒子会朝着不同的方向前进。这导致较少的定向蚀刻,蚀刻过程获得更多的化学特性。选择性增加,蚀刻轮廓更加各向同性。通过在硅蚀刻期间侧壁的钝化,实现了各向异性的蚀刻轮廓。因此,蚀刻室内的氧气与磨出的硅反应形成二氧化硅,二氧化硅沉积垂直侧壁。由于离子轰击,水平区域上的氧化膜被去除,使得横向的蚀刻进程继续进行。 蚀刻速率取决于压力、高频发生器的功率、工艺气体、实际气体流量和晶片温度。各向异性随着高频功率的增加、压力的降低和温度的降低而增加。蚀刻工艺的均匀性取决于气体、两个电极的距离以及电极的材料。如果距离太小,等离子体不能不均匀地分散,从而导致不均匀性。如果增加电极的距离,则蚀刻速率降低,因为等离子体分布在扩大的体积中。对于电极,碳已证明是首选材料。由于氟气和氯气也会攻击碳,因此电极会产生均匀的应变等离子体,因此晶圆边缘会受到与晶圆中心相同的影响。选择性和蚀刻速率在很大程度上取决于工艺气体。对于硅和硅化合物,主要使用氟气和氯气。

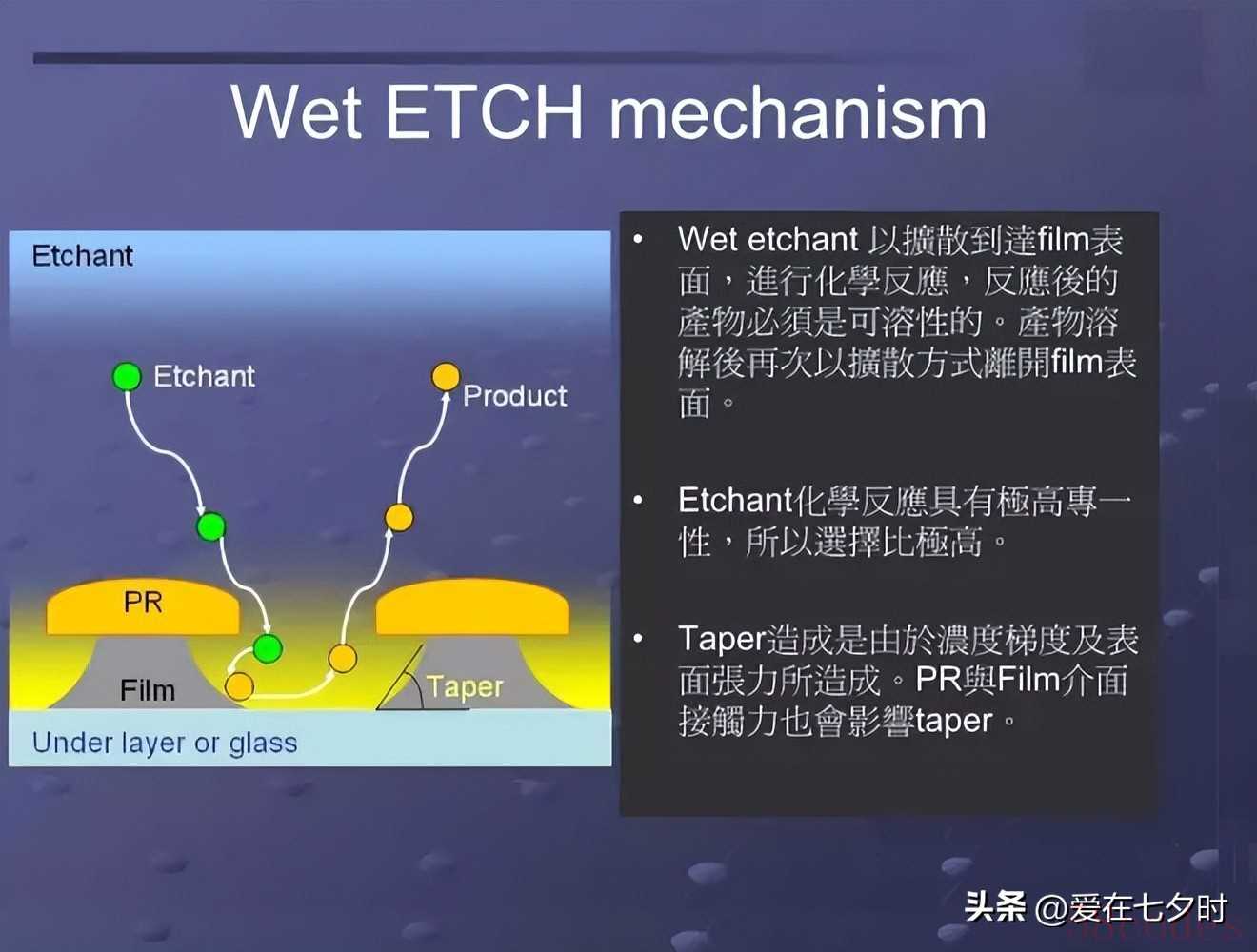

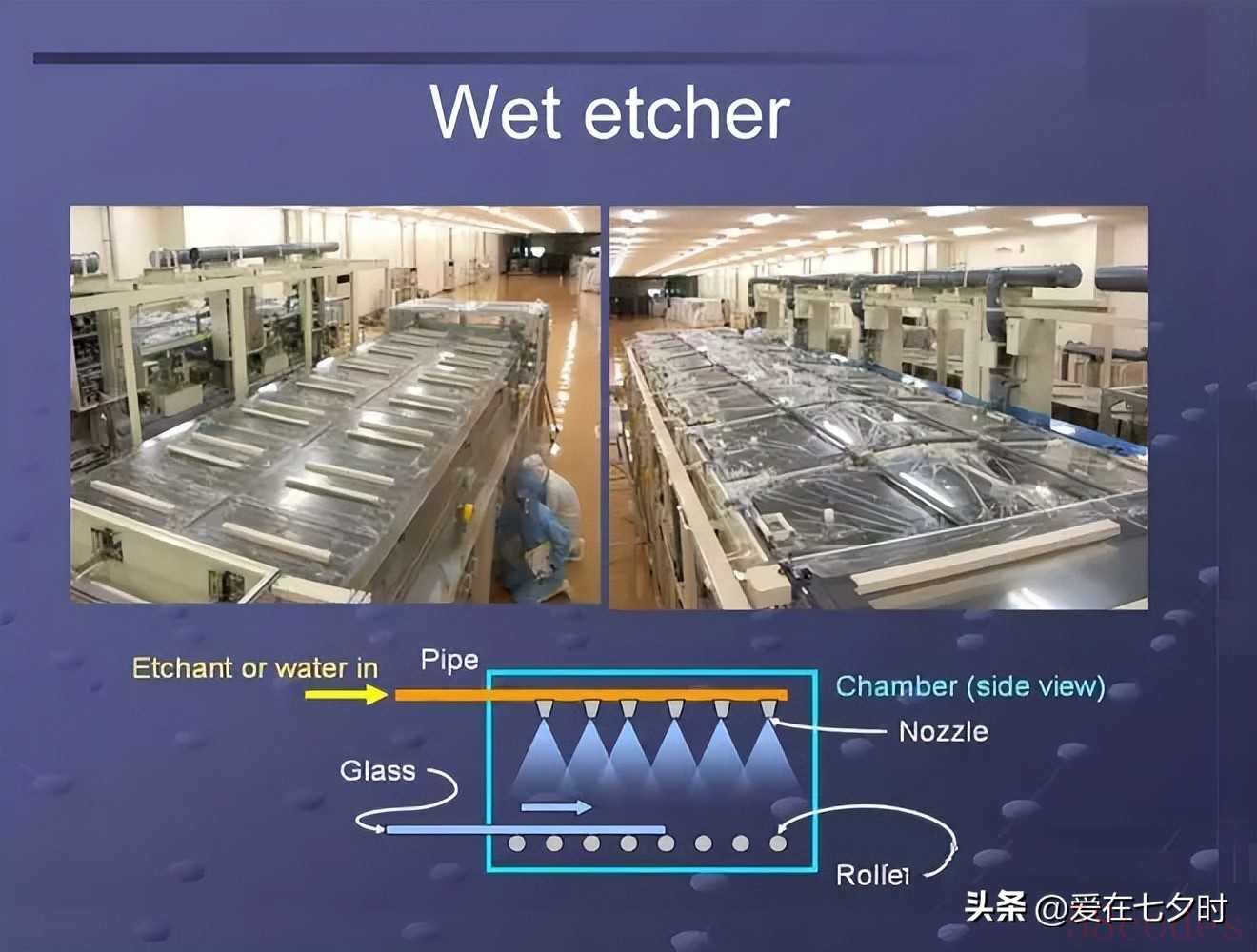

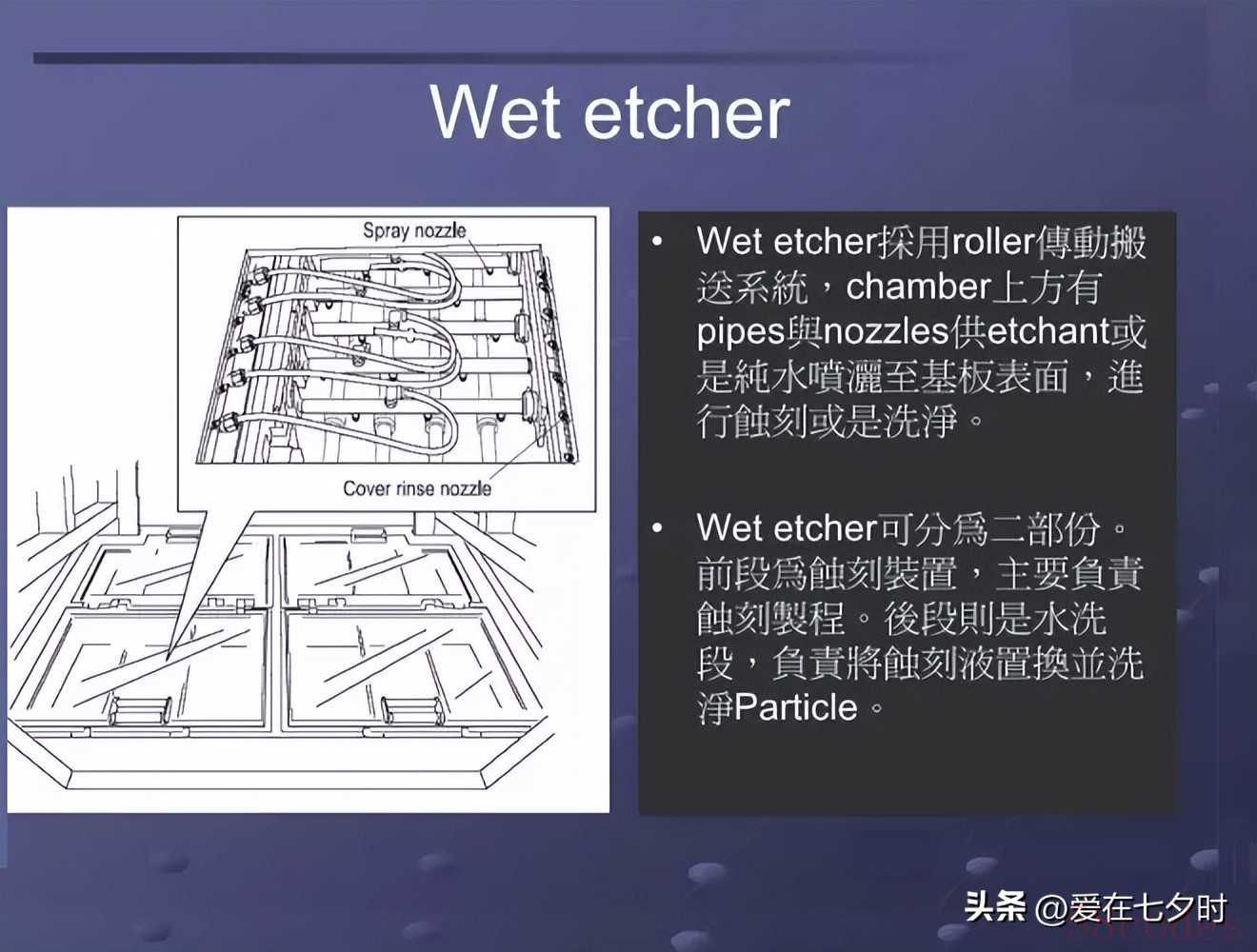

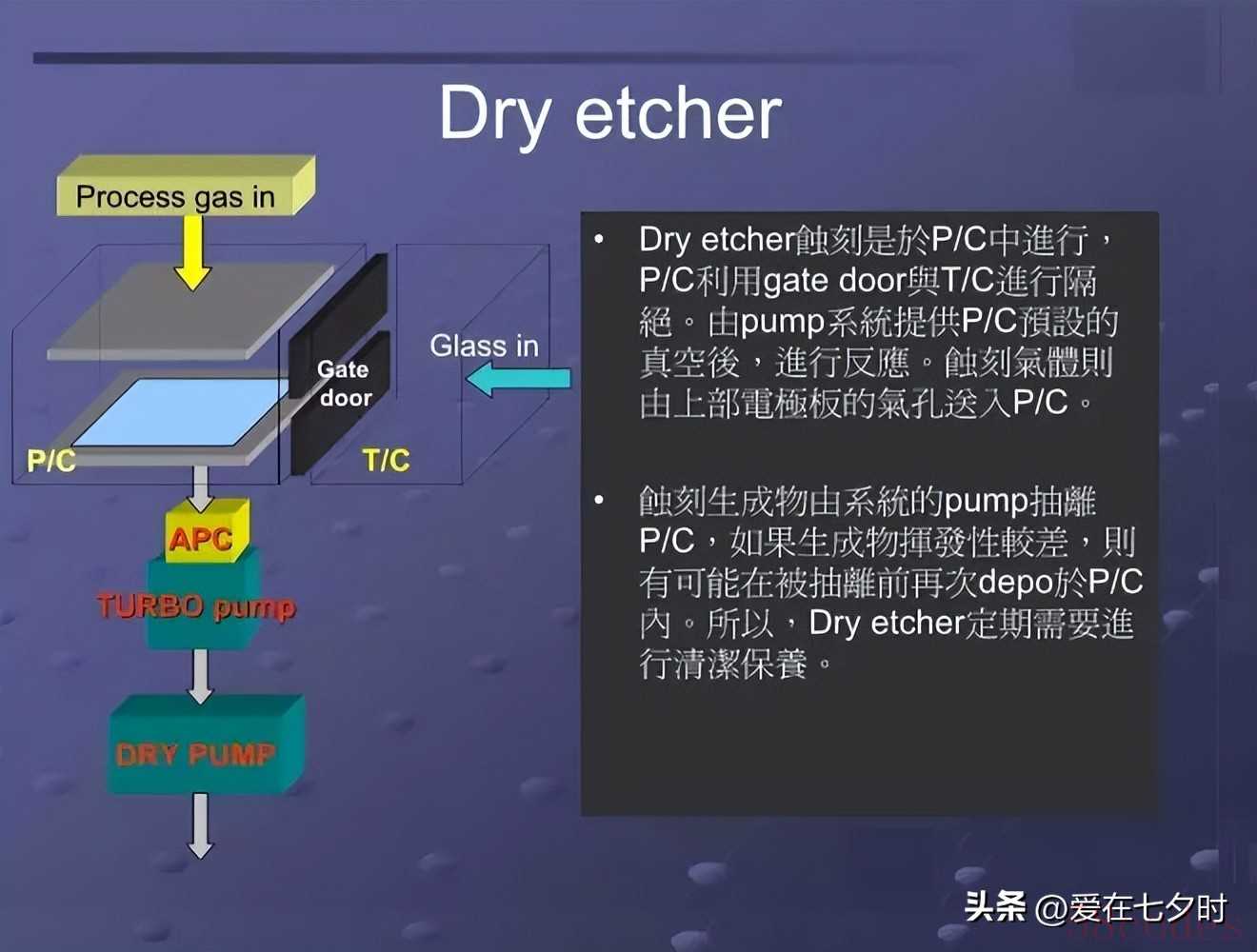

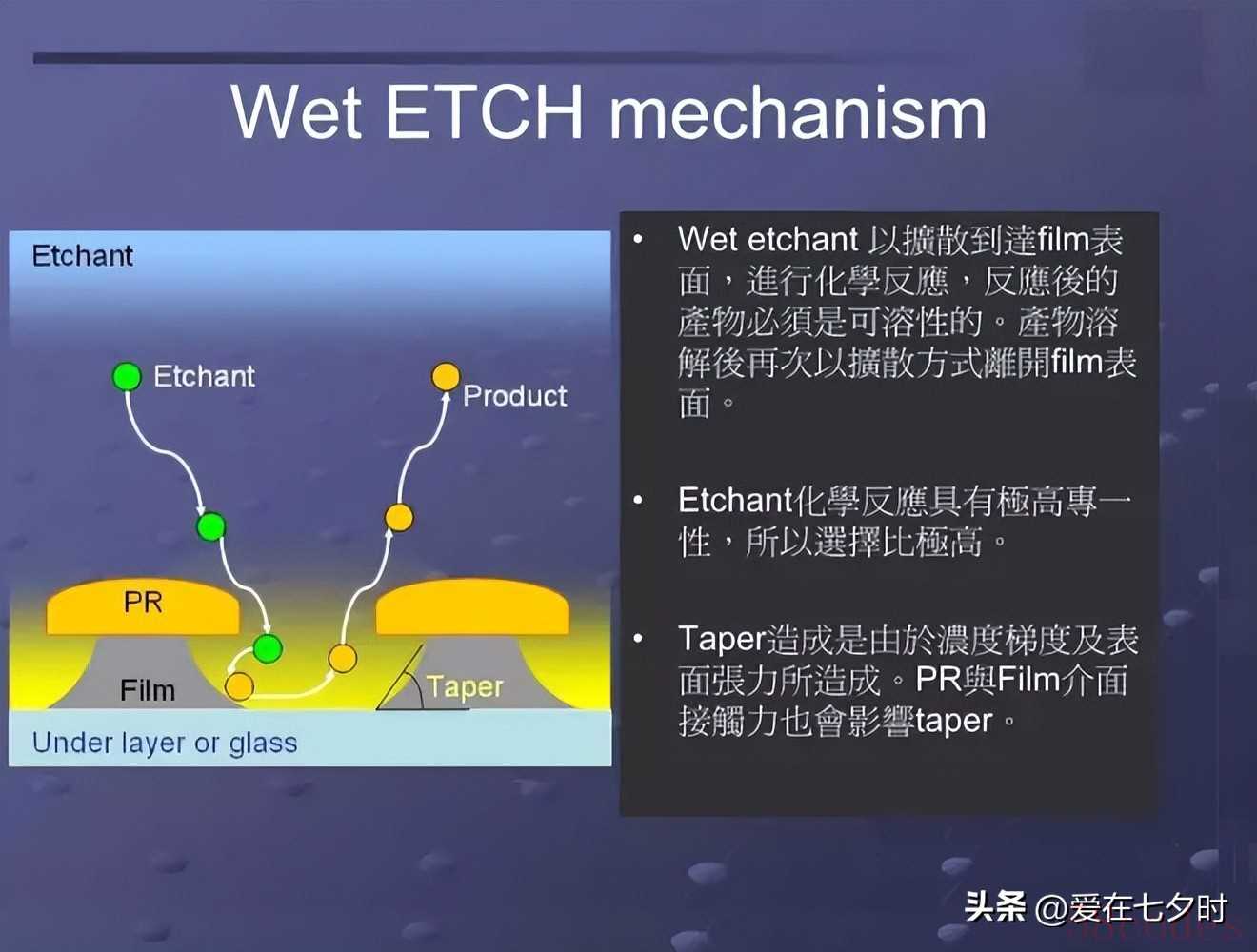

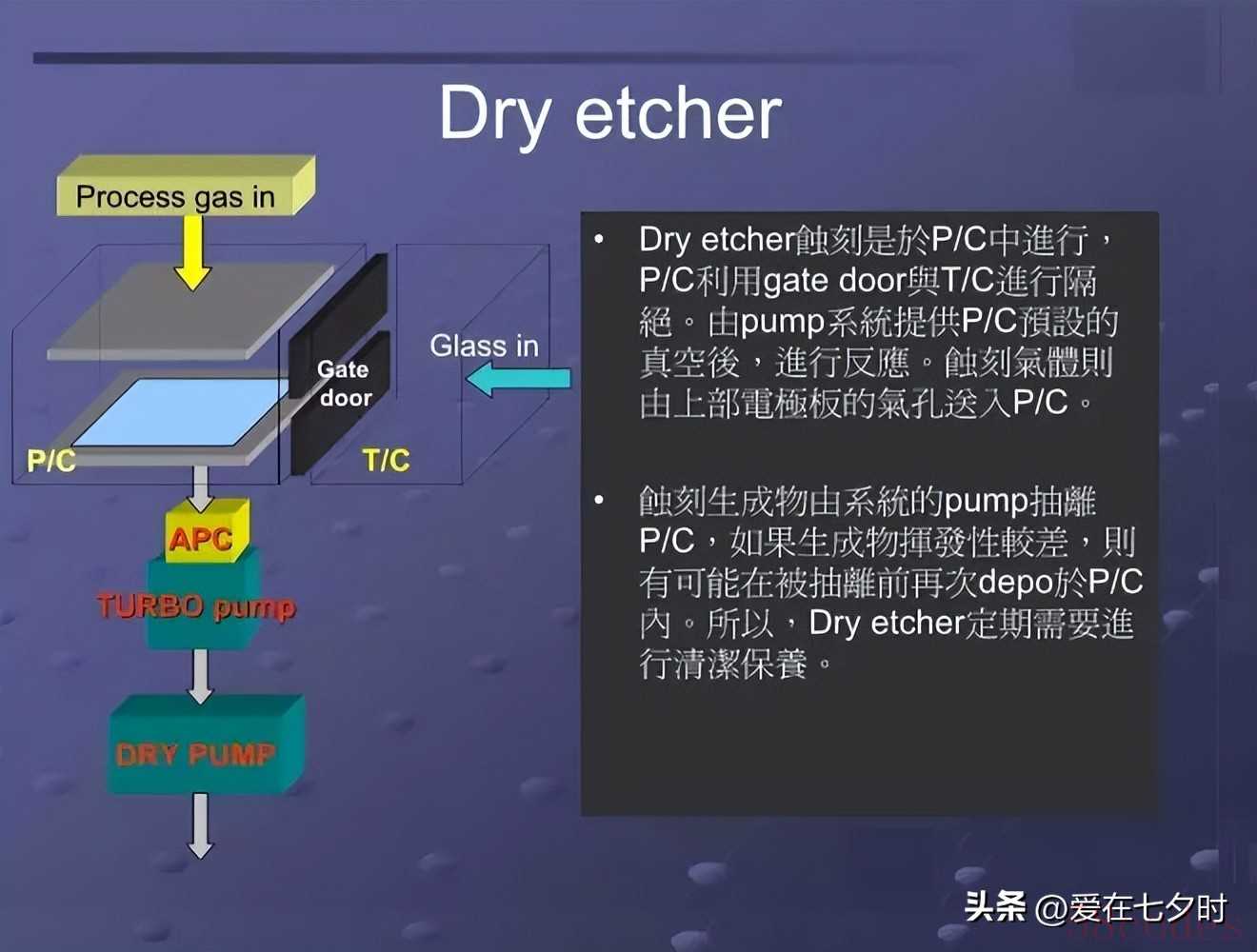

蚀刻速率取决于压力、高频发生器的功率、工艺气体、实际气体流量和晶片温度。各向异性随着高频功率的增加、压力的降低和温度的降低而增加。蚀刻工艺的均匀性取决于气体、两个电极的距离以及电极的材料。如果距离太小,等离子体不能不均匀地分散,从而导致不均匀性。如果增加电极的距离,则蚀刻速率降低,因为等离子体分布在扩大的体积中。对于电极,碳已证明是首选材料。由于氟气和氯气也会攻击碳,因此电极会产生均匀的应变等离子体,因此晶圆边缘会受到与晶圆中心相同的影响。选择性和蚀刻速率在很大程度上取决于工艺气体。对于硅和硅化合物,主要使用氟气和氯气。 蚀刻工艺不限于一种气体、气体混合物或固定工艺参数。例如,可以首先以高蚀刻速率和低选择性去除多晶硅上的原生氧化物,而随后以相对于下方层的更高选择性蚀刻多晶硅。三、“刻蚀”工艺的原理1、湿法刻蚀(1)原理利用化学溶液与半导体材料之间的化学反应来去除材料。将晶圆放入特定的化学试剂中,试剂与晶圆表面的物质发生反应,生成可溶解的产物,从而达到刻蚀的目的。例如,对于硅材料的刻蚀,常用的化学试剂可以是氢氧化钾(KOH)溶液。硅与KOH和水反应,生成硅酸钾和氢气。(2)特点湿法刻蚀具有成本低、设备简单的优点。但它对材料的选择性相对较差,在刻蚀过程中可能会对不需要刻蚀的部分也产生一定的侵蚀,并且难以精确控制刻蚀的深度和图案的边缘质量。2、干法刻蚀(1)原理主要依靠等离子体与半导体材料反应进行刻蚀。在低压环境下,通过射频电源激发气体,产生等离子体。等离子体中的活性粒子(如离子、自由基等)与晶圆表面的材料碰撞,发生反应,生成挥发性物质,这些物质被抽气系统带走,实现材料的去除。例如,采用氟基气体(如CF₄)进行硅刻蚀时,氟自由基与硅反应生成四氟化硅气体。(2)特点干法刻蚀的优点是刻蚀速度快、分辨率高、各向异性好,能够实现非常精细的图案刻蚀,并且对材料的选择性可以通过调整气体组分和工艺参数来控制。但是干法刻蚀设备复杂、成本高。

蚀刻工艺不限于一种气体、气体混合物或固定工艺参数。例如,可以首先以高蚀刻速率和低选择性去除多晶硅上的原生氧化物,而随后以相对于下方层的更高选择性蚀刻多晶硅。三、“刻蚀”工艺的原理1、湿法刻蚀(1)原理利用化学溶液与半导体材料之间的化学反应来去除材料。将晶圆放入特定的化学试剂中,试剂与晶圆表面的物质发生反应,生成可溶解的产物,从而达到刻蚀的目的。例如,对于硅材料的刻蚀,常用的化学试剂可以是氢氧化钾(KOH)溶液。硅与KOH和水反应,生成硅酸钾和氢气。(2)特点湿法刻蚀具有成本低、设备简单的优点。但它对材料的选择性相对较差,在刻蚀过程中可能会对不需要刻蚀的部分也产生一定的侵蚀,并且难以精确控制刻蚀的深度和图案的边缘质量。2、干法刻蚀(1)原理主要依靠等离子体与半导体材料反应进行刻蚀。在低压环境下,通过射频电源激发气体,产生等离子体。等离子体中的活性粒子(如离子、自由基等)与晶圆表面的材料碰撞,发生反应,生成挥发性物质,这些物质被抽气系统带走,实现材料的去除。例如,采用氟基气体(如CF₄)进行硅刻蚀时,氟自由基与硅反应生成四氟化硅气体。(2)特点干法刻蚀的优点是刻蚀速度快、分辨率高、各向异性好,能够实现非常精细的图案刻蚀,并且对材料的选择性可以通过调整气体组分和工艺参数来控制。但是干法刻蚀设备复杂、成本高。 四、“刻蚀”工艺的历史发展1、早期阶段(1950s-1960s)湿法刻蚀主导:使用酸/碱溶液(如HF、HNO₃)进行简单图形化。局限性:各向同性刻蚀导致钻蚀,难以满足高精度需求。2、干法刻蚀兴起(1970s-1980s)等离子体刻蚀(1970s):引入射频(RF)激发气体等离子体(如CF₄/O₂),实现各向异性刻蚀。反应离子刻蚀(RIE, 1980s):结合物理离子轰击与化学反应,提升刻蚀精度和深宽比。应用驱动:集成电路(IC)向微米级发展,湿法无法满足需求。典型应用: CMOS工艺3、高精度与新材料(1990s-2000s)高密度等离子体刻蚀(HDP):如ICP(电感耦合等离子体)、ECR(电子回旋共振),实现更高刻蚀速率和均匀性。新型刻蚀气体:开发Cl₂、HBr等气体以适配铜互连、低介电常数材料。典型应用:3D NAND存储芯片。挑战:深硅刻蚀(如MEMS器件)需求推动Bosch工艺(交替沉积/刻蚀)。4、纳米时代(2010s至今)原子层刻蚀(ALE):逐原子层去除,实现超高精度(<1nm)。定向自组装(DSA):结合光刻与刻蚀,突破传统分辨率限制。典型应用:5nm逻辑芯片、SiC功率器件。绿色刻蚀:减少全氟化合物(PFCs)排放,发展环保工艺。

四、“刻蚀”工艺的历史发展1、早期阶段(1950s-1960s)湿法刻蚀主导:使用酸/碱溶液(如HF、HNO₃)进行简单图形化。局限性:各向同性刻蚀导致钻蚀,难以满足高精度需求。2、干法刻蚀兴起(1970s-1980s)等离子体刻蚀(1970s):引入射频(RF)激发气体等离子体(如CF₄/O₂),实现各向异性刻蚀。反应离子刻蚀(RIE, 1980s):结合物理离子轰击与化学反应,提升刻蚀精度和深宽比。应用驱动:集成电路(IC)向微米级发展,湿法无法满足需求。典型应用: CMOS工艺3、高精度与新材料(1990s-2000s)高密度等离子体刻蚀(HDP):如ICP(电感耦合等离子体)、ECR(电子回旋共振),实现更高刻蚀速率和均匀性。新型刻蚀气体:开发Cl₂、HBr等气体以适配铜互连、低介电常数材料。典型应用:3D NAND存储芯片。挑战:深硅刻蚀(如MEMS器件)需求推动Bosch工艺(交替沉积/刻蚀)。4、纳米时代(2010s至今)原子层刻蚀(ALE):逐原子层去除,实现超高精度(<1nm)。定向自组装(DSA):结合光刻与刻蚀,突破传统分辨率限制。典型应用:5nm逻辑芯片、SiC功率器件。绿色刻蚀:减少全氟化合物(PFCs)排放,发展环保工艺。 五、“刻蚀”工艺的作用1、形成电路图案半导体器件是由各种复杂的电路图案组成的,刻蚀工艺可以将光刻工艺定义的图案精确地转移到晶圆上。例如,在制造集成电路时,需要将设计的电路图案从光刻版转移到晶圆表面的光刻胶上,然后通过刻蚀工艺去除未被光刻胶保护的部分,从而形成与设计图案一致的电路结构。2、决定器件性能刻蚀工艺的质量直接影响半导体器件的性能。如果刻蚀深度控制不准确,可能会导致器件的电学性能下降。例如,在制造MOS(金属 - 氧化物 - 半导体)晶体管时,栅极氧化层的厚度需要精确控制,而这依赖于刻蚀工艺对氧化层厚度的精确处理。如果氧化层过厚或过薄,都会影响晶体管的阈值电压和电流特性。3、影响良率精确的刻蚀工艺对于提高半导体制造的良率至关重要。在大规模生产中,任何微小的刻蚀缺陷都可能导致大量的芯片失效。例如,刻蚀过程中的不均匀性可能会造成芯片局部区域的尺寸偏差,导致芯片在后续测试中无法正常工作,从而降低良率。

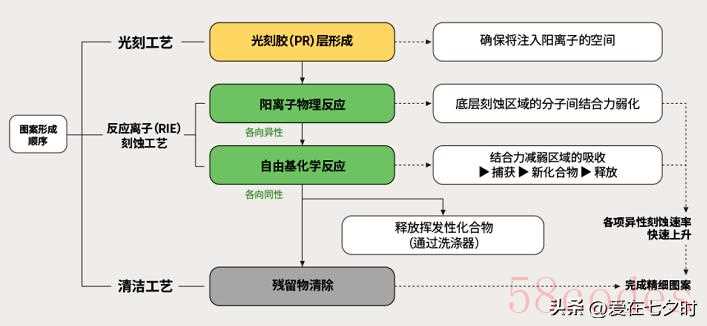

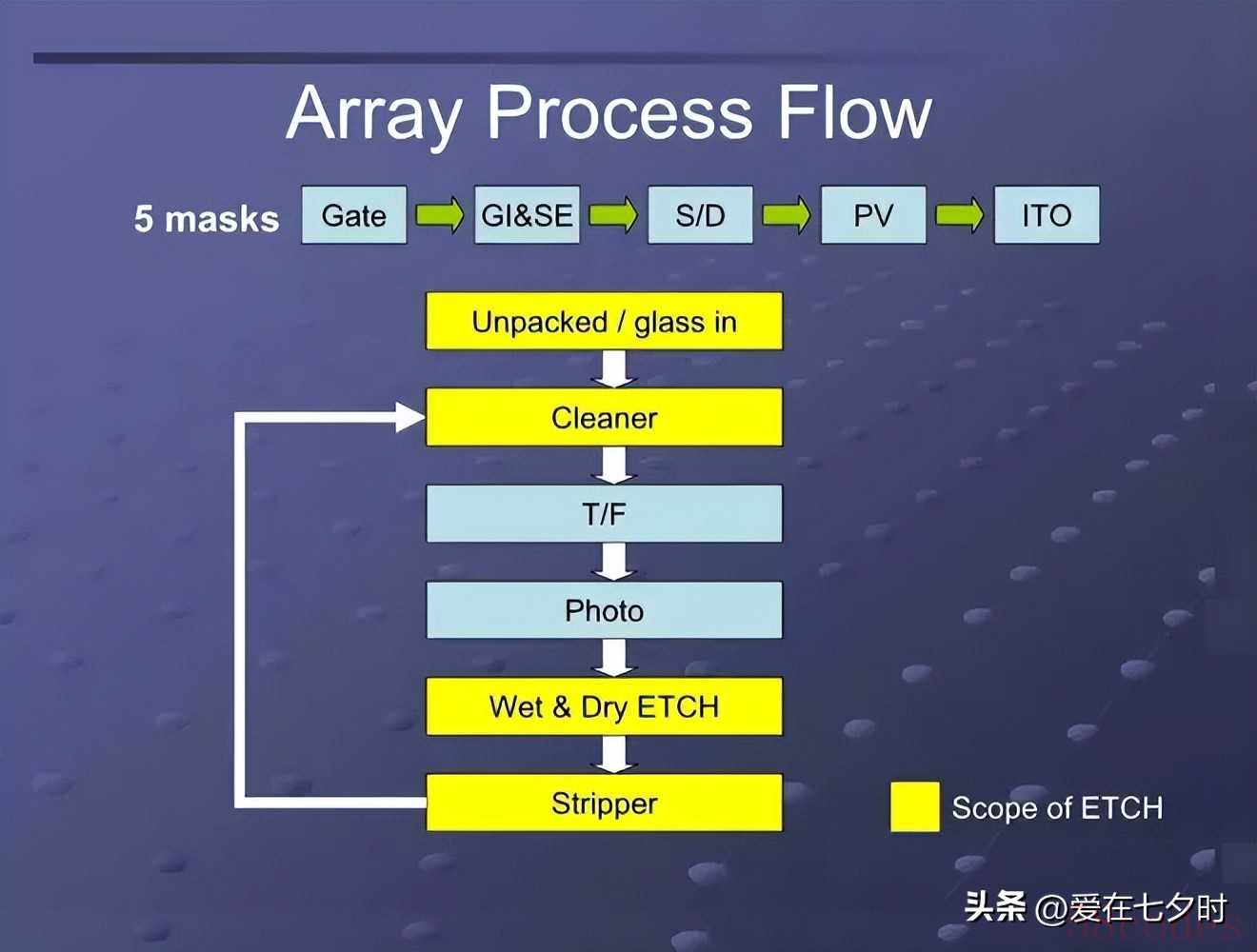

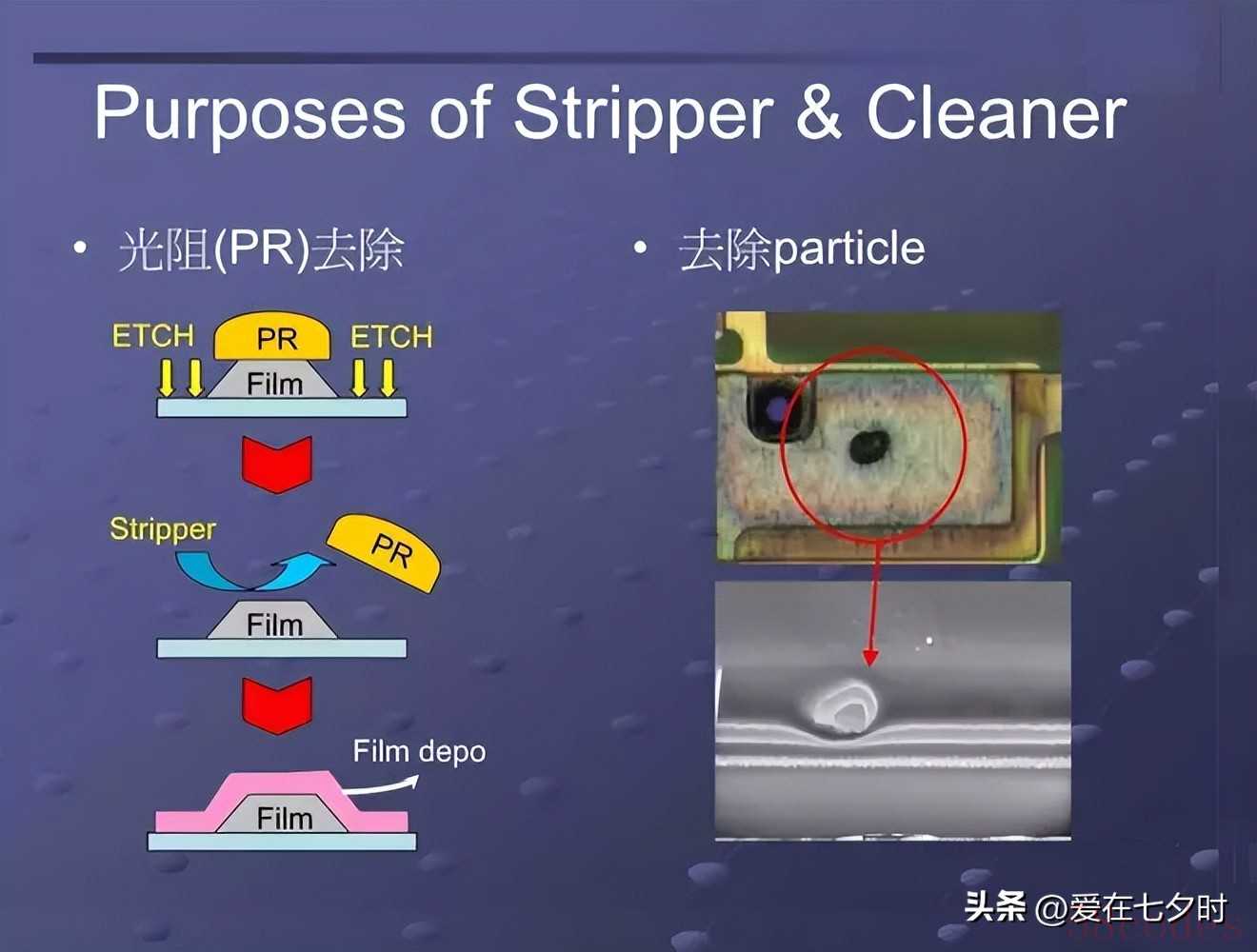

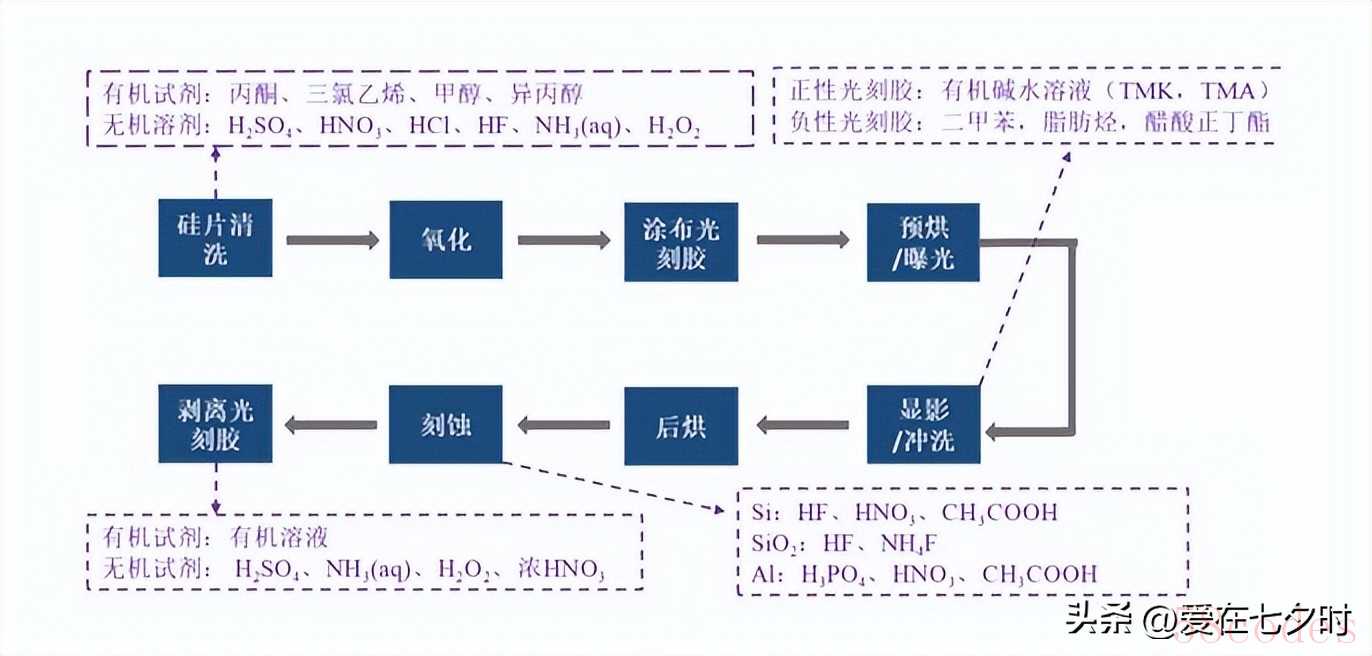

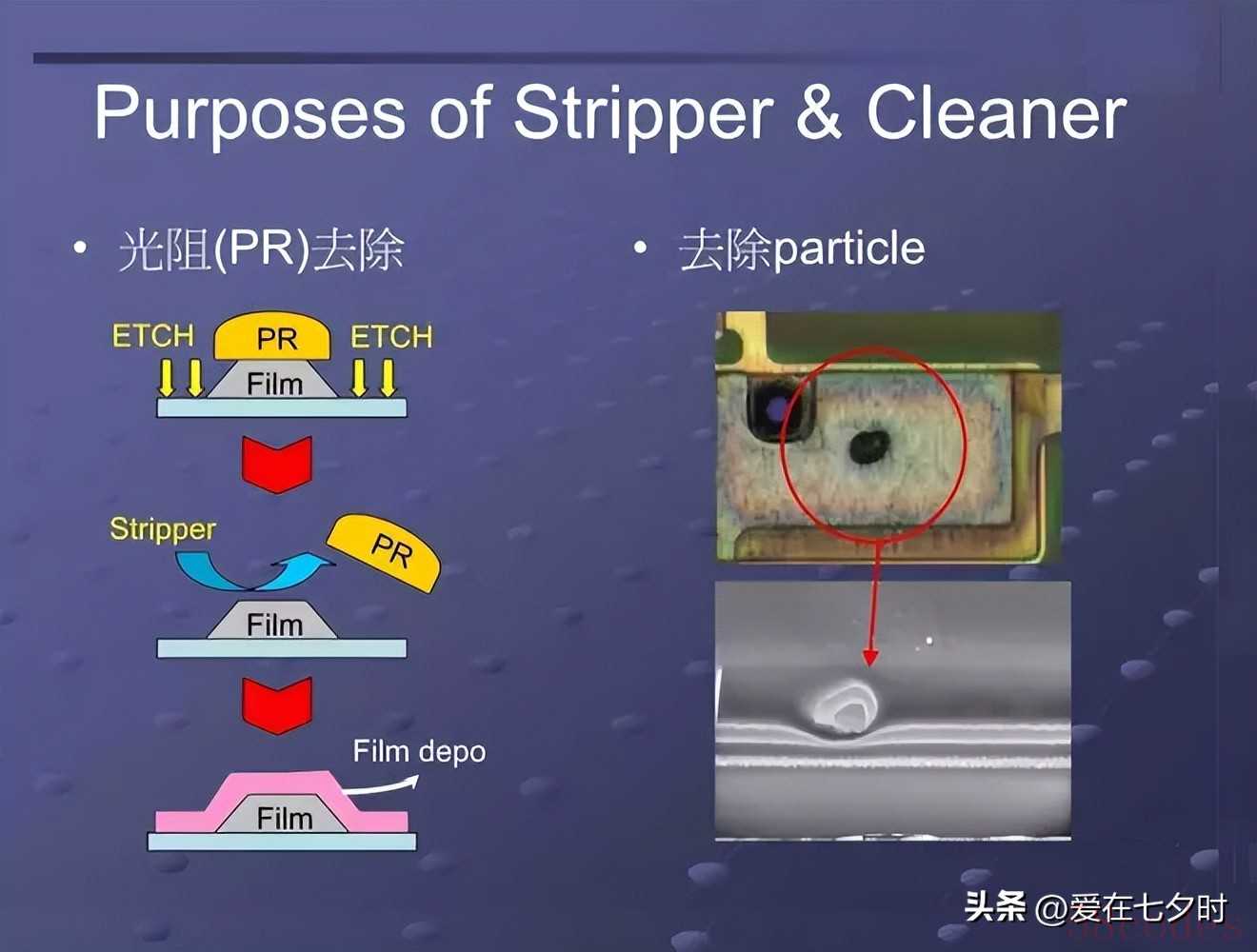

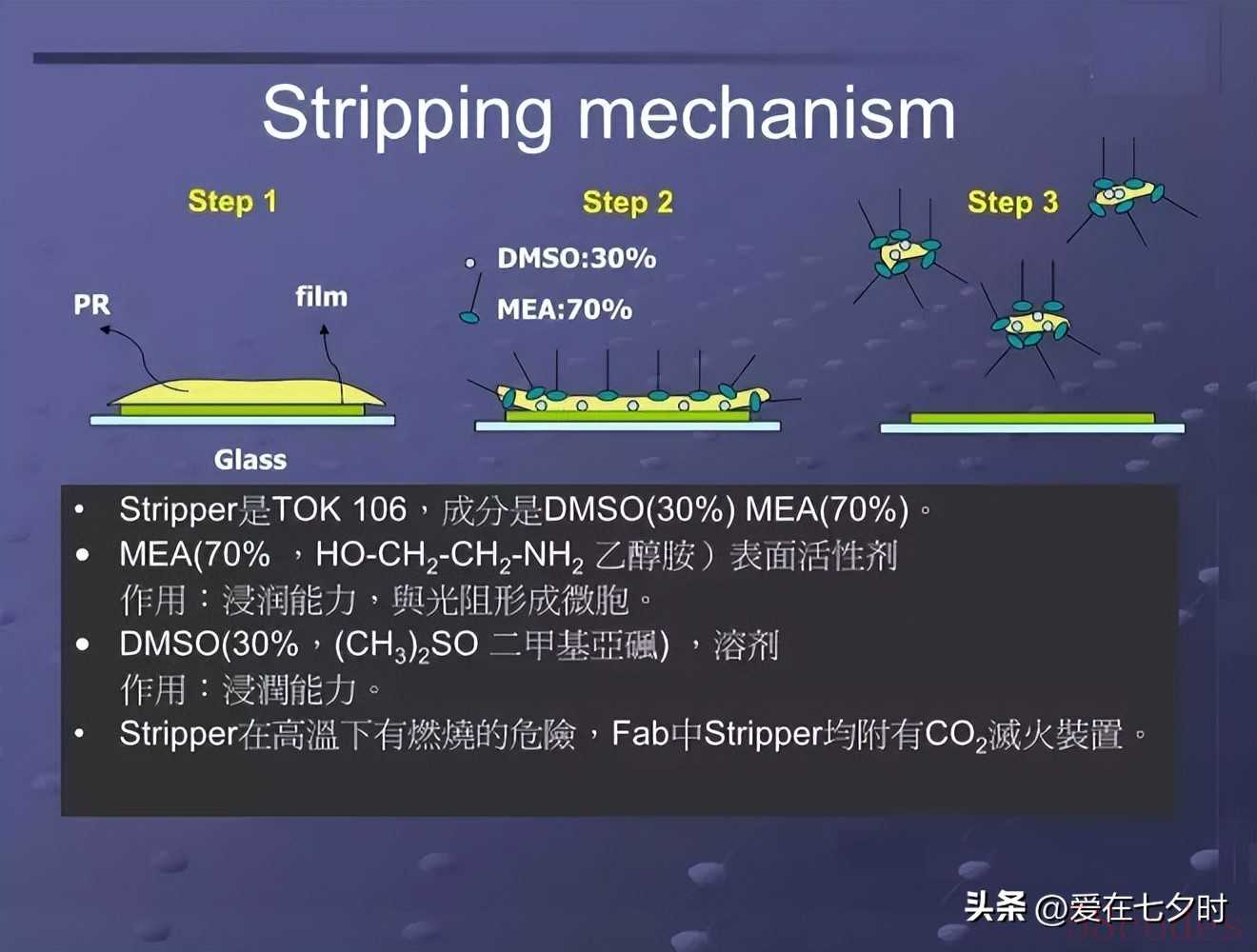

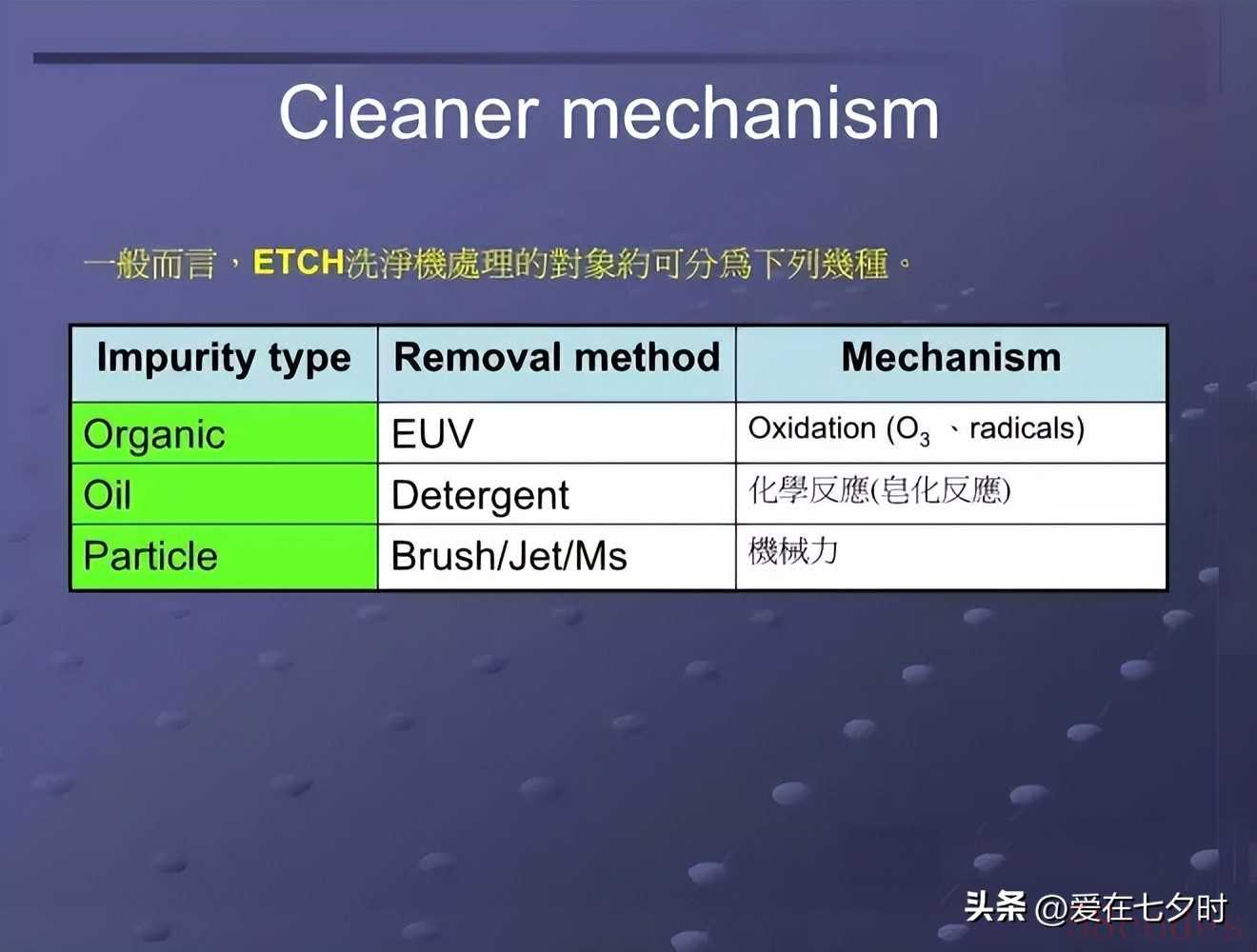

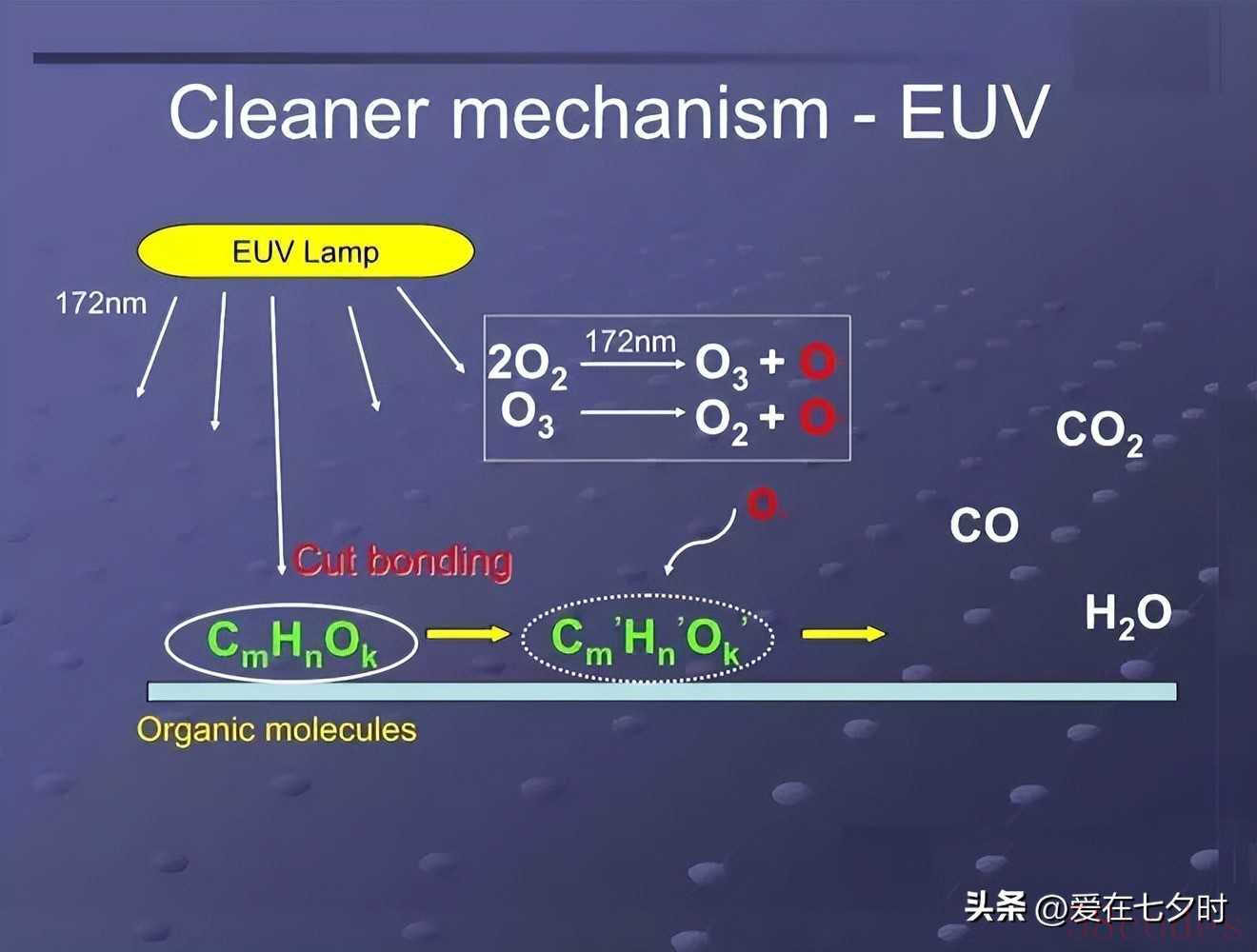

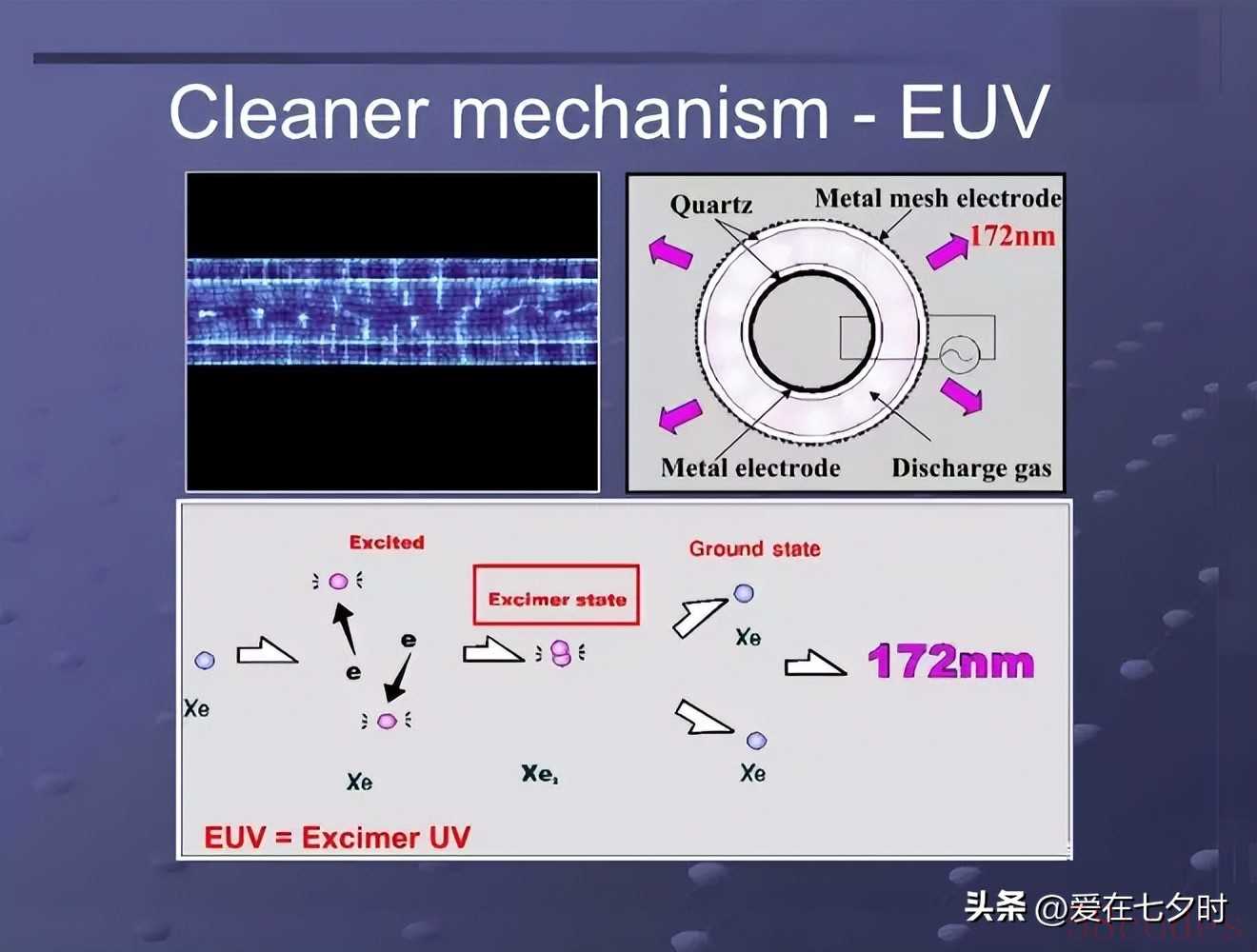

五、“刻蚀”工艺的作用1、形成电路图案半导体器件是由各种复杂的电路图案组成的,刻蚀工艺可以将光刻工艺定义的图案精确地转移到晶圆上。例如,在制造集成电路时,需要将设计的电路图案从光刻版转移到晶圆表面的光刻胶上,然后通过刻蚀工艺去除未被光刻胶保护的部分,从而形成与设计图案一致的电路结构。2、决定器件性能刻蚀工艺的质量直接影响半导体器件的性能。如果刻蚀深度控制不准确,可能会导致器件的电学性能下降。例如,在制造MOS(金属 - 氧化物 - 半导体)晶体管时,栅极氧化层的厚度需要精确控制,而这依赖于刻蚀工艺对氧化层厚度的精确处理。如果氧化层过厚或过薄,都会影响晶体管的阈值电压和电流特性。3、影响良率精确的刻蚀工艺对于提高半导体制造的良率至关重要。在大规模生产中,任何微小的刻蚀缺陷都可能导致大量的芯片失效。例如,刻蚀过程中的不均匀性可能会造成芯片局部区域的尺寸偏差,导致芯片在后续测试中无法正常工作,从而降低良率。 六、“刻蚀”工艺的流程1、预处理在进行刻蚀之前,需要对晶圆进行清洗和预处理,以去除表面的杂质和自然氧化层。清洗过程通常包括多个步骤,如使用化学溶剂清洗、超纯水冲洗等,确保晶圆表面干净、平整。2、光刻光刻是刻蚀工艺的前序步骤。在晶圆表面涂上一层光刻胶,然后使用光刻机将设计好的图案曝光在光刻胶上。曝光后的光刻胶在显影液中进行处理,未曝光的部分被溶解掉,露出晶圆表面需要刻蚀的区域。3、刻蚀根据选择的刻蚀方式(湿法或干法),将晶圆放入相应的刻蚀设备中进行刻蚀。在刻蚀过程中,需要严格控制刻蚀的时间、温度、压力、气体流量(针对干法刻蚀)等参数,以确保刻蚀的效果符合要求。4、后处理刻蚀完成后,需要对晶圆进行清洗和检测。清洗过程主要是去除残留的光刻胶和刻蚀产物,检测过程包括对刻蚀深度、图案尺寸和形状等参数的测量,确保刻蚀后的图案符合设计要求。

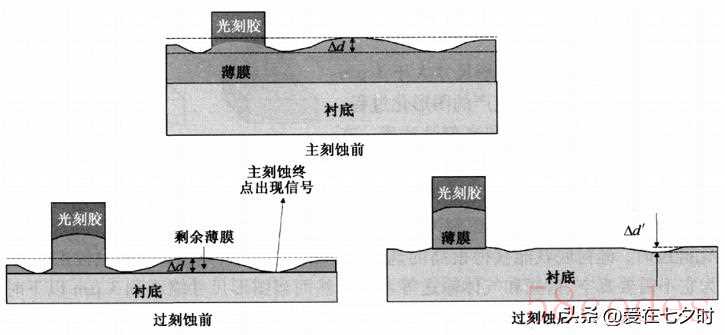

六、“刻蚀”工艺的流程1、预处理在进行刻蚀之前,需要对晶圆进行清洗和预处理,以去除表面的杂质和自然氧化层。清洗过程通常包括多个步骤,如使用化学溶剂清洗、超纯水冲洗等,确保晶圆表面干净、平整。2、光刻光刻是刻蚀工艺的前序步骤。在晶圆表面涂上一层光刻胶,然后使用光刻机将设计好的图案曝光在光刻胶上。曝光后的光刻胶在显影液中进行处理,未曝光的部分被溶解掉,露出晶圆表面需要刻蚀的区域。3、刻蚀根据选择的刻蚀方式(湿法或干法),将晶圆放入相应的刻蚀设备中进行刻蚀。在刻蚀过程中,需要严格控制刻蚀的时间、温度、压力、气体流量(针对干法刻蚀)等参数,以确保刻蚀的效果符合要求。4、后处理刻蚀完成后,需要对晶圆进行清洗和检测。清洗过程主要是去除残留的光刻胶和刻蚀产物,检测过程包括对刻蚀深度、图案尺寸和形状等参数的测量,确保刻蚀后的图案符合设计要求。 七、“刻蚀”工艺的参数1、刻蚀速率(Etch Rate)定义:单位时间内材料被去除的厚度(如 nm/min 或 Å/min)。影响因素:干法:等离子体功率、气体流量、压力、离子能量。湿法:溶液浓度、温度、搅拌速度。重要性:速率过高可能导致过刻蚀,过低则影响生产效率。2、刻蚀均匀性(Uniformity)定义:刻蚀速率在晶圆表面或图形间的差异(通常用百分比表示,如 ±5%)。影响因素:干法:等离子体分布、气体流动均匀性、腔体设计。湿法:溶液搅拌、晶圆旋转、浸泡时间。关键指标:片内均匀性(WIW)和片间均匀性(WTW)。3、选择性(Selectivity)定义:刻蚀目标材料与掩膜或下层材料的刻蚀速率比(如 Si:SiO₂ = 50:1)。影响因素:干法:气体化学(如 Cl₂ 对 Si 高选择性)、离子能量。湿法:溶液成分(如 HF 对 SiO₂ 高选择性)。重要性:高选择性保护掩膜和底层结构,减少损伤。

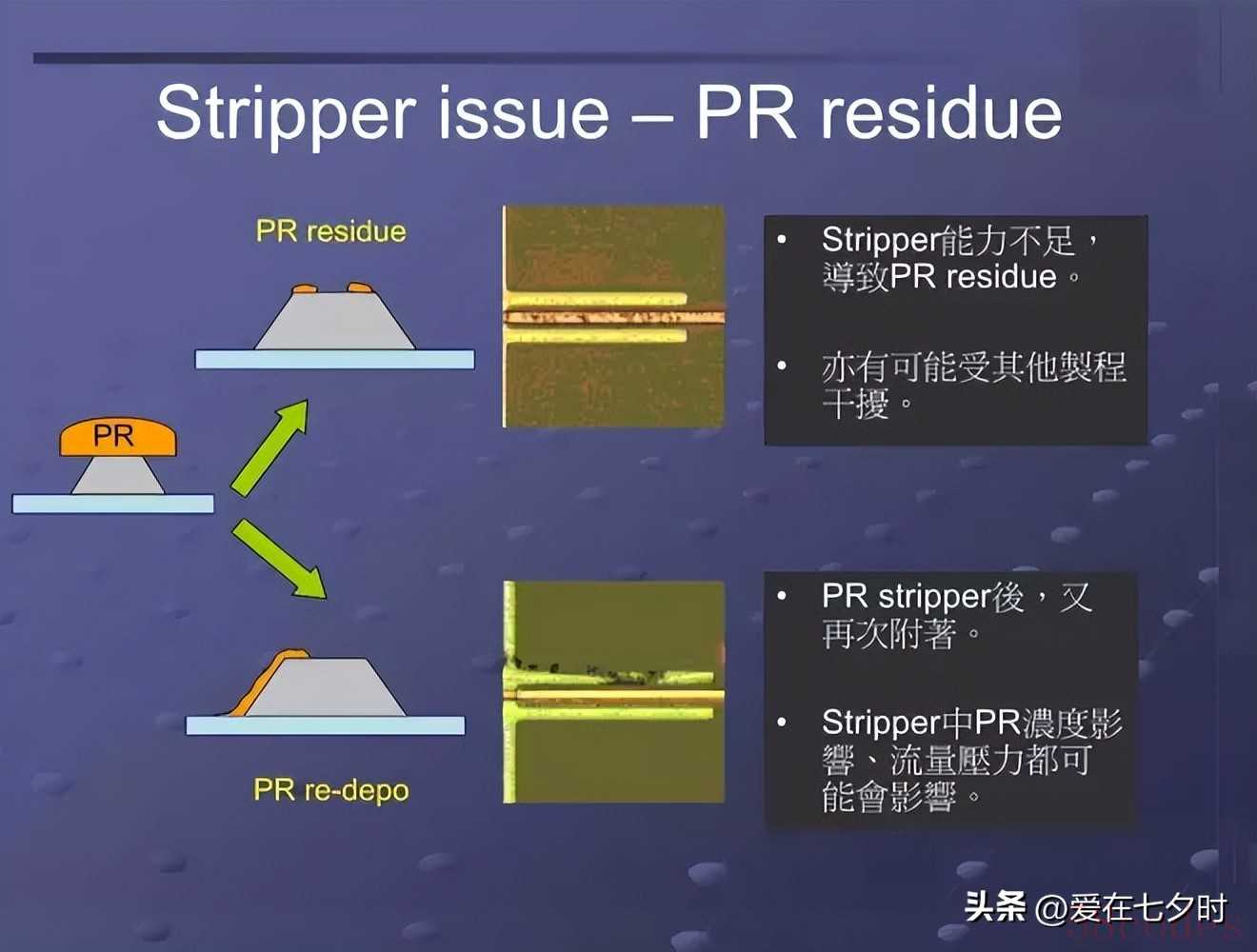

七、“刻蚀”工艺的参数1、刻蚀速率(Etch Rate)定义:单位时间内材料被去除的厚度(如 nm/min 或 Å/min)。影响因素:干法:等离子体功率、气体流量、压力、离子能量。湿法:溶液浓度、温度、搅拌速度。重要性:速率过高可能导致过刻蚀,过低则影响生产效率。2、刻蚀均匀性(Uniformity)定义:刻蚀速率在晶圆表面或图形间的差异(通常用百分比表示,如 ±5%)。影响因素:干法:等离子体分布、气体流动均匀性、腔体设计。湿法:溶液搅拌、晶圆旋转、浸泡时间。关键指标:片内均匀性(WIW)和片间均匀性(WTW)。3、选择性(Selectivity)定义:刻蚀目标材料与掩膜或下层材料的刻蚀速率比(如 Si:SiO₂ = 50:1)。影响因素:干法:气体化学(如 Cl₂ 对 Si 高选择性)、离子能量。湿法:溶液成分(如 HF 对 SiO₂ 高选择性)。重要性:高选择性保护掩膜和底层结构,减少损伤。 4、各向异性(Anisotropy)定义:刻蚀的垂直方向与横向刻蚀的比例(完全各向异性 = 无横向刻蚀)。影响因素:干法:离子轰击方向(如 RIE)、侧壁钝化(如 Bosch 工艺)。湿法:通常各向同性(横向钻蚀明显)。应用场景:高深宽比结构(如 TSV、FinFET)需高各向异性。5、刻蚀剖面(Etch Profile)定义:刻蚀后结构的侧壁形貌(如垂直、锥形、倒梯形)。关键参数:侧壁角度:90°为理想垂直剖面。粗糙度:侧壁光滑度(影响器件性能)。控制方法:调整离子能量、气体化学、温度。6、负载效应(Loading Effect)定义:刻蚀速率因图形密度或面积不同而变化的现象。类型:宏观负载效应:晶圆间刻蚀速率差异。微观负载效应:图形密集区与稀疏区速率差异。解决方案:优化等离子体均匀性、调节气体流量。7、残留物与聚合物(Residue/Polymer)定义:刻蚀后残留的副产物(如碳氟聚合物)。来源:干法:气体反应不完全(如 CF₄ 刻蚀 Si 产生 SiF₄ 和 CₓFᵧ)。湿法:金属离子残留(如 Al 刻蚀后 Cu 污染)。清除方法:O₂ 等离子体灰化、湿法清洗(RCA)。下面是干法刻蚀和湿法刻蚀的关键参数控制表格:

4、各向异性(Anisotropy)定义:刻蚀的垂直方向与横向刻蚀的比例(完全各向异性 = 无横向刻蚀)。影响因素:干法:离子轰击方向(如 RIE)、侧壁钝化(如 Bosch 工艺)。湿法:通常各向同性(横向钻蚀明显)。应用场景:高深宽比结构(如 TSV、FinFET)需高各向异性。5、刻蚀剖面(Etch Profile)定义:刻蚀后结构的侧壁形貌(如垂直、锥形、倒梯形)。关键参数:侧壁角度:90°为理想垂直剖面。粗糙度:侧壁光滑度(影响器件性能)。控制方法:调整离子能量、气体化学、温度。6、负载效应(Loading Effect)定义:刻蚀速率因图形密度或面积不同而变化的现象。类型:宏观负载效应:晶圆间刻蚀速率差异。微观负载效应:图形密集区与稀疏区速率差异。解决方案:优化等离子体均匀性、调节气体流量。7、残留物与聚合物(Residue/Polymer)定义:刻蚀后残留的副产物(如碳氟聚合物)。来源:干法:气体反应不完全(如 CF₄ 刻蚀 Si 产生 SiF₄ 和 CₓFᵧ)。湿法:金属离子残留(如 Al 刻蚀后 Cu 污染)。清除方法:O₂ 等离子体灰化、湿法清洗(RCA)。下面是干法刻蚀和湿法刻蚀的关键参数控制表格: 八、“刻蚀”工艺技术的详细介绍以下就是要跟大家分享的具体内容,希望感兴趣的朋友可以加入我的“知识星球”,一起多多交流学习:

八、“刻蚀”工艺技术的详细介绍以下就是要跟大家分享的具体内容,希望感兴趣的朋友可以加入我的“知识星球”,一起多多交流学习:

因为本PPT章节太多,剩下部分如有朋友有需要,可加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!文末有加入“星球”方式,欢迎加入后一起交流学习。九、“刻蚀”工艺当前面对的挑战1、3D NAND的高深宽比(HAR)刻蚀挑战(1)深孔/深槽刻蚀128层及以上3D NAND需刻蚀深宽比>60:1的通道孔(如7μm深、<100nm宽),离子和反应物传输困难,易导致刻蚀不完全或侧壁扭曲。(2)掩膜消耗与选择比高能离子轰击加速掩膜(如碳硬掩膜)消耗,需开发新型掩膜材料或优化刻蚀气体配比。2、先进制程的高精度要求(1)纳米级刻蚀控制在5nm及以下制程中,刻蚀精度需达到原子级别(如<1nm),传统刻蚀方法难以满足要求。原子层刻蚀(ALE)虽能实现单原子层去除,但工艺复杂且成本高昂。(2)关键尺寸(CD)均匀性多重曝光技术(如EUV+SAQP)要求刻蚀后线宽误差控制在±0.5nm以内,否则影响器件性能。3、国产化技术瓶颈(1)高端设备依赖进口中国刻蚀设备的国产化率在2025年已达到约20%,但7nm以下刻蚀设备仍由泛林(Lam)、东京电子(TEL)垄断,国产设备(如中微CCP)在5nm验证中但市占率不足10%,(2)关键零部件卡脖子射频电源、真空泵等核心部件依赖欧美日供应链。

因为本PPT章节太多,剩下部分如有朋友有需要,可加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!文末有加入“星球”方式,欢迎加入后一起交流学习。九、“刻蚀”工艺当前面对的挑战1、3D NAND的高深宽比(HAR)刻蚀挑战(1)深孔/深槽刻蚀128层及以上3D NAND需刻蚀深宽比>60:1的通道孔(如7μm深、<100nm宽),离子和反应物传输困难,易导致刻蚀不完全或侧壁扭曲。(2)掩膜消耗与选择比高能离子轰击加速掩膜(如碳硬掩膜)消耗,需开发新型掩膜材料或优化刻蚀气体配比。2、先进制程的高精度要求(1)纳米级刻蚀控制在5nm及以下制程中,刻蚀精度需达到原子级别(如<1nm),传统刻蚀方法难以满足要求。原子层刻蚀(ALE)虽能实现单原子层去除,但工艺复杂且成本高昂。(2)关键尺寸(CD)均匀性多重曝光技术(如EUV+SAQP)要求刻蚀后线宽误差控制在±0.5nm以内,否则影响器件性能。3、国产化技术瓶颈(1)高端设备依赖进口中国刻蚀设备的国产化率在2025年已达到约20%,但7nm以下刻蚀设备仍由泛林(Lam)、东京电子(TEL)垄断,国产设备(如中微CCP)在5nm验证中但市占率不足10%,(2)关键零部件卡脖子射频电源、真空泵等核心部件依赖欧美日供应链。 十、“刻蚀”工艺未来的发展刻蚀技术就像医生手中的手术刀,其技术演化直接决定摩尔定律乃至后摩尔时代芯片制造的发展趋势,新型材料和智能化Al的运用将形成新的驱动力推动刻蚀技术发展。原子层刻蚀(ALE):单原子层精度控制。AI工艺优化:通过大数据实时调节刻蚀参数。新型等离子体源/新型气体化学:如超低温ICP(-50°C)减少损伤,NF₃/Ar混合气体提升SiC刻蚀速率(>2μm/min)。总之,由于“刻蚀”工艺技术是紧随光刻技术而来,它涉及使用化学或物理方法去除硅片上多余的材料,以形成所需的图案。这一过程中,精确控制刻蚀的深度和位置至关重要。刻蚀技术的发展同样对提高芯片质量和性能起着关键作用。

十、“刻蚀”工艺未来的发展刻蚀技术就像医生手中的手术刀,其技术演化直接决定摩尔定律乃至后摩尔时代芯片制造的发展趋势,新型材料和智能化Al的运用将形成新的驱动力推动刻蚀技术发展。原子层刻蚀(ALE):单原子层精度控制。AI工艺优化:通过大数据实时调节刻蚀参数。新型等离子体源/新型气体化学:如超低温ICP(-50°C)减少损伤,NF₃/Ar混合气体提升SiC刻蚀速率(>2μm/min)。总之,由于“刻蚀”工艺技术是紧随光刻技术而来,它涉及使用化学或物理方法去除硅片上多余的材料,以形成所需的图案。这一过程中,精确控制刻蚀的深度和位置至关重要。刻蚀技术的发展同样对提高芯片质量和性能起着关键作用。 -----End-----免责声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

-----End-----免责声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

一、“刻蚀”工艺的介绍刻蚀,英文为Etch,它是半导体制造工艺,微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。是与光刻相联系的图形化(pattern)处理的一种主要工艺。所谓刻蚀,实际上狭义理解就是光刻腐蚀,先通过光刻将光刻胶进行光刻曝光处理,然后通过其它方式实现腐蚀处理掉所需除去的部分。刻蚀是用化学或物理方法有选择地从硅片表面去除不需要的材料的过程,其基本目标是在涂胶的硅片上正确地复制掩模图形。随着微制造工艺的发展,广义上来讲,刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称,成为微加工制造的一种普适叫法。

一、“刻蚀”工艺的介绍刻蚀,英文为Etch,它是半导体制造工艺,微电子IC制造工艺以及微纳制造工艺中的一种相当重要的步骤。是与光刻相联系的图形化(pattern)处理的一种主要工艺。所谓刻蚀,实际上狭义理解就是光刻腐蚀,先通过光刻将光刻胶进行光刻曝光处理,然后通过其它方式实现腐蚀处理掉所需除去的部分。刻蚀是用化学或物理方法有选择地从硅片表面去除不需要的材料的过程,其基本目标是在涂胶的硅片上正确地复制掩模图形。随着微制造工艺的发展,广义上来讲,刻蚀成了通过溶液、反应离子或其它机械方式来剥离、去除材料的一种统称,成为微加工制造的一种普适叫法。 二、“刻蚀”工艺的分类刻蚀按大类来分,主要分为:湿法刻蚀和干法刻蚀两种,下面表格简单对两种刻蚀方法进行对比:

二、“刻蚀”工艺的分类刻蚀按大类来分,主要分为:湿法刻蚀和干法刻蚀两种,下面表格简单对两种刻蚀方法进行对比: 其中,在干法蚀刻中,气体受高频(主要为 13.56 MHz 或 2.45 GHz)激发。在 1 到 100 Pa 的压力下,其平均自由程为几毫米到几厘米。主要有三种类型的干法蚀刻:• 物理干法蚀刻:加速粒子对晶圆表面的物理磨损;• 化学干法蚀刻:气体与晶圆表面发生化学反应;• 化学物理干法蚀刻:具有化学特性的物理蚀刻工艺;

其中,在干法蚀刻中,气体受高频(主要为 13.56 MHz 或 2.45 GHz)激发。在 1 到 100 Pa 的压力下,其平均自由程为几毫米到几厘米。主要有三种类型的干法蚀刻:• 物理干法蚀刻:加速粒子对晶圆表面的物理磨损;• 化学干法蚀刻:气体与晶圆表面发生化学反应;• 化学物理干法蚀刻:具有化学特性的物理蚀刻工艺; 1、离子束蚀刻离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对各向异性的。选择性低,因为其对各个层没有差异。气体和被打磨出的材料被真空泵排出,但是,由于反应产物不是气态的,颗粒会沉积在晶片或室壁上。

1、离子束蚀刻离子束蚀刻 (Ion beam etch) 是一种物理干法蚀刻工艺。由此,氩离子以约1至3keV的离子束辐射到表面上。由于离子的能量,它们会撞击表面的材料。晶圆垂直或倾斜入离子束,蚀刻过程是绝对各向异性的。选择性低,因为其对各个层没有差异。气体和被打磨出的材料被真空泵排出,但是,由于反应产物不是气态的,颗粒会沉积在晶片或室壁上。 为避免颗粒,将第二种气体引入腔室。该气体与氩离子发生反应并引起物理化学蚀刻过程。部分气体与表面反应,但也与打磨出的颗粒反应形成气态副产物。几乎所有材料都可以用这种方法蚀刻。由于垂直辐射,垂直壁上的磨损非常低(高各向异性)。然而,由于低选择性和低蚀刻速率,该工艺在当今的半导体制造中很少使用。2、等离子刻蚀等离子刻蚀(Plasma etch)是一种绝对化学刻蚀工艺(化学干法刻蚀,Chemical dry etch)。优点是晶圆表面不会被加速离子损坏。由于蚀刻气体的可移动颗粒,蚀刻轮廓是各向同性的,因此该方法用于去除整个膜层(如热氧化后的背面清洁)。一种用于等离子体蚀刻的反应器类型是下游反应器。从而通过碰撞电离在2.45GHz的高频下点燃等离子体,碰撞电离的位置与晶片分离。

为避免颗粒,将第二种气体引入腔室。该气体与氩离子发生反应并引起物理化学蚀刻过程。部分气体与表面反应,但也与打磨出的颗粒反应形成气态副产物。几乎所有材料都可以用这种方法蚀刻。由于垂直辐射,垂直壁上的磨损非常低(高各向异性)。然而,由于低选择性和低蚀刻速率,该工艺在当今的半导体制造中很少使用。2、等离子刻蚀等离子刻蚀(Plasma etch)是一种绝对化学刻蚀工艺(化学干法刻蚀,Chemical dry etch)。优点是晶圆表面不会被加速离子损坏。由于蚀刻气体的可移动颗粒,蚀刻轮廓是各向同性的,因此该方法用于去除整个膜层(如热氧化后的背面清洁)。一种用于等离子体蚀刻的反应器类型是下游反应器。从而通过碰撞电离在2.45GHz的高频下点燃等离子体,碰撞电离的位置与晶片分离。 在气体放电区域,由于冲击存在各种颗粒,其中有自由基。自由基是具有不饱和电子的中性原子或分子,因此非常活泼。作为中性气体,例如四氟甲烷CF4被引入气体放电区并分离成CF2和氟分子F2。类似地,氟可以通过添加氧气 O2 从 CF4 中分离出来:2 CF4 + O2 --->2 COF2 + 2 F2氟分子可以通过气体放电区的能量分裂成两个单独的氟原子:每个氟原子都是一个氟自由基,因为每个原子都有七个价电子,并希望实现惰性气体构型。除了中性自由基之外,还有几个部分带电的粒子(CF+4、CF+3、CF+2、...)。然后,所有粒子、自由基等都通过陶瓷管进入蚀刻室。带电粒子可以通过提取光栅从蚀刻室中阻挡或者在它们形成中性分子的途中重新组合。氟自由基也有部分重组,但足以到达蚀刻室,在晶圆表面发生反应并引起化学磨损。其他中性粒子不是蚀刻过程的一部分,并且与反应产物一样被耗尽。可在等离子蚀刻中蚀刻的薄膜示例: • 硅: Si + 4F---> SiF4 • 二氧化硅: SiO2 + 4F---> SiF4 + O2 • 氮化硅: Si3N4 + 12F---> 3SiF4 + 2N23.反应离子蚀刻蚀刻特性: 选择性、蚀刻轮廓、蚀刻速率、均匀性、可重复性 - 均可以在反应离子蚀刻 (Reactive ion etch) 中非常精确地控制。各向同性蚀刻轮廓以及各向异性是可能的。因此,RIE 工艺是一种化学物理蚀刻工艺,是半导体制造中用于构造各种薄膜的最重要工艺。 在工艺室内,晶圆放置在高频电极(HF电极)上。通过碰撞电离产生等离子体,其中出现自由电子和带正电的离子。如果 HF 电极处于正电压,则自由电子会在其上积聚,并且由于它们的电子亲和力而无法再次离开电极。因此,电极充电至 -1000 V(偏置电压)。不能跟随快速交变场的慢离子向带负电的电极移动。

在气体放电区域,由于冲击存在各种颗粒,其中有自由基。自由基是具有不饱和电子的中性原子或分子,因此非常活泼。作为中性气体,例如四氟甲烷CF4被引入气体放电区并分离成CF2和氟分子F2。类似地,氟可以通过添加氧气 O2 从 CF4 中分离出来:2 CF4 + O2 --->2 COF2 + 2 F2氟分子可以通过气体放电区的能量分裂成两个单独的氟原子:每个氟原子都是一个氟自由基,因为每个原子都有七个价电子,并希望实现惰性气体构型。除了中性自由基之外,还有几个部分带电的粒子(CF+4、CF+3、CF+2、...)。然后,所有粒子、自由基等都通过陶瓷管进入蚀刻室。带电粒子可以通过提取光栅从蚀刻室中阻挡或者在它们形成中性分子的途中重新组合。氟自由基也有部分重组,但足以到达蚀刻室,在晶圆表面发生反应并引起化学磨损。其他中性粒子不是蚀刻过程的一部分,并且与反应产物一样被耗尽。可在等离子蚀刻中蚀刻的薄膜示例: • 硅: Si + 4F---> SiF4 • 二氧化硅: SiO2 + 4F---> SiF4 + O2 • 氮化硅: Si3N4 + 12F---> 3SiF4 + 2N23.反应离子蚀刻蚀刻特性: 选择性、蚀刻轮廓、蚀刻速率、均匀性、可重复性 - 均可以在反应离子蚀刻 (Reactive ion etch) 中非常精确地控制。各向同性蚀刻轮廓以及各向异性是可能的。因此,RIE 工艺是一种化学物理蚀刻工艺,是半导体制造中用于构造各种薄膜的最重要工艺。 在工艺室内,晶圆放置在高频电极(HF电极)上。通过碰撞电离产生等离子体,其中出现自由电子和带正电的离子。如果 HF 电极处于正电压,则自由电子会在其上积聚,并且由于它们的电子亲和力而无法再次离开电极。因此,电极充电至 -1000 V(偏置电压)。不能跟随快速交变场的慢离子向带负电的电极移动。 如果离子的平均自由程高,则粒子以几乎垂直的方向撞击晶片表面。因此,材料被加速离子(物理蚀刻)从表面击出,此外,一些粒子与表面发生化学反应。横向侧壁不受影响,因此没有磨损并且蚀刻轮廓保持各向异性。选择性不是太小,但是,由于物理蚀刻进程,它也不是太大。此外,晶圆表面会被加速离子损坏,必须通过热退火进行固化。 蚀刻工艺的化学部分是通过自由基与表面以及物理铣削材料的反应来完成的,这样它就不会像离子束蚀刻那样重新沉积到晶圆或腔室壁上。通过增加蚀刻室中的压力,颗粒的平均自由程减少。因此会有更多的碰撞,因此粒子会朝着不同的方向前进。这导致较少的定向蚀刻,蚀刻过程获得更多的化学特性。选择性增加,蚀刻轮廓更加各向同性。通过在硅蚀刻期间侧壁的钝化,实现了各向异性的蚀刻轮廓。因此,蚀刻室内的氧气与磨出的硅反应形成二氧化硅,二氧化硅沉积垂直侧壁。由于离子轰击,水平区域上的氧化膜被去除,使得横向的蚀刻进程继续进行。

如果离子的平均自由程高,则粒子以几乎垂直的方向撞击晶片表面。因此,材料被加速离子(物理蚀刻)从表面击出,此外,一些粒子与表面发生化学反应。横向侧壁不受影响,因此没有磨损并且蚀刻轮廓保持各向异性。选择性不是太小,但是,由于物理蚀刻进程,它也不是太大。此外,晶圆表面会被加速离子损坏,必须通过热退火进行固化。 蚀刻工艺的化学部分是通过自由基与表面以及物理铣削材料的反应来完成的,这样它就不会像离子束蚀刻那样重新沉积到晶圆或腔室壁上。通过增加蚀刻室中的压力,颗粒的平均自由程减少。因此会有更多的碰撞,因此粒子会朝着不同的方向前进。这导致较少的定向蚀刻,蚀刻过程获得更多的化学特性。选择性增加,蚀刻轮廓更加各向同性。通过在硅蚀刻期间侧壁的钝化,实现了各向异性的蚀刻轮廓。因此,蚀刻室内的氧气与磨出的硅反应形成二氧化硅,二氧化硅沉积垂直侧壁。由于离子轰击,水平区域上的氧化膜被去除,使得横向的蚀刻进程继续进行。 蚀刻速率取决于压力、高频发生器的功率、工艺气体、实际气体流量和晶片温度。各向异性随着高频功率的增加、压力的降低和温度的降低而增加。蚀刻工艺的均匀性取决于气体、两个电极的距离以及电极的材料。如果距离太小,等离子体不能不均匀地分散,从而导致不均匀性。如果增加电极的距离,则蚀刻速率降低,因为等离子体分布在扩大的体积中。对于电极,碳已证明是首选材料。由于氟气和氯气也会攻击碳,因此电极会产生均匀的应变等离子体,因此晶圆边缘会受到与晶圆中心相同的影响。选择性和蚀刻速率在很大程度上取决于工艺气体。对于硅和硅化合物,主要使用氟气和氯气。

蚀刻速率取决于压力、高频发生器的功率、工艺气体、实际气体流量和晶片温度。各向异性随着高频功率的增加、压力的降低和温度的降低而增加。蚀刻工艺的均匀性取决于气体、两个电极的距离以及电极的材料。如果距离太小,等离子体不能不均匀地分散,从而导致不均匀性。如果增加电极的距离,则蚀刻速率降低,因为等离子体分布在扩大的体积中。对于电极,碳已证明是首选材料。由于氟气和氯气也会攻击碳,因此电极会产生均匀的应变等离子体,因此晶圆边缘会受到与晶圆中心相同的影响。选择性和蚀刻速率在很大程度上取决于工艺气体。对于硅和硅化合物,主要使用氟气和氯气。 蚀刻工艺不限于一种气体、气体混合物或固定工艺参数。例如,可以首先以高蚀刻速率和低选择性去除多晶硅上的原生氧化物,而随后以相对于下方层的更高选择性蚀刻多晶硅。三、“刻蚀”工艺的原理1、湿法刻蚀(1)原理利用化学溶液与半导体材料之间的化学反应来去除材料。将晶圆放入特定的化学试剂中,试剂与晶圆表面的物质发生反应,生成可溶解的产物,从而达到刻蚀的目的。例如,对于硅材料的刻蚀,常用的化学试剂可以是氢氧化钾(KOH)溶液。硅与KOH和水反应,生成硅酸钾和氢气。(2)特点湿法刻蚀具有成本低、设备简单的优点。但它对材料的选择性相对较差,在刻蚀过程中可能会对不需要刻蚀的部分也产生一定的侵蚀,并且难以精确控制刻蚀的深度和图案的边缘质量。2、干法刻蚀(1)原理主要依靠等离子体与半导体材料反应进行刻蚀。在低压环境下,通过射频电源激发气体,产生等离子体。等离子体中的活性粒子(如离子、自由基等)与晶圆表面的材料碰撞,发生反应,生成挥发性物质,这些物质被抽气系统带走,实现材料的去除。例如,采用氟基气体(如CF₄)进行硅刻蚀时,氟自由基与硅反应生成四氟化硅气体。(2)特点干法刻蚀的优点是刻蚀速度快、分辨率高、各向异性好,能够实现非常精细的图案刻蚀,并且对材料的选择性可以通过调整气体组分和工艺参数来控制。但是干法刻蚀设备复杂、成本高。

蚀刻工艺不限于一种气体、气体混合物或固定工艺参数。例如,可以首先以高蚀刻速率和低选择性去除多晶硅上的原生氧化物,而随后以相对于下方层的更高选择性蚀刻多晶硅。三、“刻蚀”工艺的原理1、湿法刻蚀(1)原理利用化学溶液与半导体材料之间的化学反应来去除材料。将晶圆放入特定的化学试剂中,试剂与晶圆表面的物质发生反应,生成可溶解的产物,从而达到刻蚀的目的。例如,对于硅材料的刻蚀,常用的化学试剂可以是氢氧化钾(KOH)溶液。硅与KOH和水反应,生成硅酸钾和氢气。(2)特点湿法刻蚀具有成本低、设备简单的优点。但它对材料的选择性相对较差,在刻蚀过程中可能会对不需要刻蚀的部分也产生一定的侵蚀,并且难以精确控制刻蚀的深度和图案的边缘质量。2、干法刻蚀(1)原理主要依靠等离子体与半导体材料反应进行刻蚀。在低压环境下,通过射频电源激发气体,产生等离子体。等离子体中的活性粒子(如离子、自由基等)与晶圆表面的材料碰撞,发生反应,生成挥发性物质,这些物质被抽气系统带走,实现材料的去除。例如,采用氟基气体(如CF₄)进行硅刻蚀时,氟自由基与硅反应生成四氟化硅气体。(2)特点干法刻蚀的优点是刻蚀速度快、分辨率高、各向异性好,能够实现非常精细的图案刻蚀,并且对材料的选择性可以通过调整气体组分和工艺参数来控制。但是干法刻蚀设备复杂、成本高。 四、“刻蚀”工艺的历史发展1、早期阶段(1950s-1960s)湿法刻蚀主导:使用酸/碱溶液(如HF、HNO₃)进行简单图形化。局限性:各向同性刻蚀导致钻蚀,难以满足高精度需求。2、干法刻蚀兴起(1970s-1980s)等离子体刻蚀(1970s):引入射频(RF)激发气体等离子体(如CF₄/O₂),实现各向异性刻蚀。反应离子刻蚀(RIE, 1980s):结合物理离子轰击与化学反应,提升刻蚀精度和深宽比。应用驱动:集成电路(IC)向微米级发展,湿法无法满足需求。典型应用: CMOS工艺3、高精度与新材料(1990s-2000s)高密度等离子体刻蚀(HDP):如ICP(电感耦合等离子体)、ECR(电子回旋共振),实现更高刻蚀速率和均匀性。新型刻蚀气体:开发Cl₂、HBr等气体以适配铜互连、低介电常数材料。典型应用:3D NAND存储芯片。挑战:深硅刻蚀(如MEMS器件)需求推动Bosch工艺(交替沉积/刻蚀)。4、纳米时代(2010s至今)原子层刻蚀(ALE):逐原子层去除,实现超高精度(<1nm)。定向自组装(DSA):结合光刻与刻蚀,突破传统分辨率限制。典型应用:5nm逻辑芯片、SiC功率器件。绿色刻蚀:减少全氟化合物(PFCs)排放,发展环保工艺。

四、“刻蚀”工艺的历史发展1、早期阶段(1950s-1960s)湿法刻蚀主导:使用酸/碱溶液(如HF、HNO₃)进行简单图形化。局限性:各向同性刻蚀导致钻蚀,难以满足高精度需求。2、干法刻蚀兴起(1970s-1980s)等离子体刻蚀(1970s):引入射频(RF)激发气体等离子体(如CF₄/O₂),实现各向异性刻蚀。反应离子刻蚀(RIE, 1980s):结合物理离子轰击与化学反应,提升刻蚀精度和深宽比。应用驱动:集成电路(IC)向微米级发展,湿法无法满足需求。典型应用: CMOS工艺3、高精度与新材料(1990s-2000s)高密度等离子体刻蚀(HDP):如ICP(电感耦合等离子体)、ECR(电子回旋共振),实现更高刻蚀速率和均匀性。新型刻蚀气体:开发Cl₂、HBr等气体以适配铜互连、低介电常数材料。典型应用:3D NAND存储芯片。挑战:深硅刻蚀(如MEMS器件)需求推动Bosch工艺(交替沉积/刻蚀)。4、纳米时代(2010s至今)原子层刻蚀(ALE):逐原子层去除,实现超高精度(<1nm)。定向自组装(DSA):结合光刻与刻蚀,突破传统分辨率限制。典型应用:5nm逻辑芯片、SiC功率器件。绿色刻蚀:减少全氟化合物(PFCs)排放,发展环保工艺。 五、“刻蚀”工艺的作用1、形成电路图案半导体器件是由各种复杂的电路图案组成的,刻蚀工艺可以将光刻工艺定义的图案精确地转移到晶圆上。例如,在制造集成电路时,需要将设计的电路图案从光刻版转移到晶圆表面的光刻胶上,然后通过刻蚀工艺去除未被光刻胶保护的部分,从而形成与设计图案一致的电路结构。2、决定器件性能刻蚀工艺的质量直接影响半导体器件的性能。如果刻蚀深度控制不准确,可能会导致器件的电学性能下降。例如,在制造MOS(金属 - 氧化物 - 半导体)晶体管时,栅极氧化层的厚度需要精确控制,而这依赖于刻蚀工艺对氧化层厚度的精确处理。如果氧化层过厚或过薄,都会影响晶体管的阈值电压和电流特性。3、影响良率精确的刻蚀工艺对于提高半导体制造的良率至关重要。在大规模生产中,任何微小的刻蚀缺陷都可能导致大量的芯片失效。例如,刻蚀过程中的不均匀性可能会造成芯片局部区域的尺寸偏差,导致芯片在后续测试中无法正常工作,从而降低良率。

五、“刻蚀”工艺的作用1、形成电路图案半导体器件是由各种复杂的电路图案组成的,刻蚀工艺可以将光刻工艺定义的图案精确地转移到晶圆上。例如,在制造集成电路时,需要将设计的电路图案从光刻版转移到晶圆表面的光刻胶上,然后通过刻蚀工艺去除未被光刻胶保护的部分,从而形成与设计图案一致的电路结构。2、决定器件性能刻蚀工艺的质量直接影响半导体器件的性能。如果刻蚀深度控制不准确,可能会导致器件的电学性能下降。例如,在制造MOS(金属 - 氧化物 - 半导体)晶体管时,栅极氧化层的厚度需要精确控制,而这依赖于刻蚀工艺对氧化层厚度的精确处理。如果氧化层过厚或过薄,都会影响晶体管的阈值电压和电流特性。3、影响良率精确的刻蚀工艺对于提高半导体制造的良率至关重要。在大规模生产中,任何微小的刻蚀缺陷都可能导致大量的芯片失效。例如,刻蚀过程中的不均匀性可能会造成芯片局部区域的尺寸偏差,导致芯片在后续测试中无法正常工作,从而降低良率。 六、“刻蚀”工艺的流程1、预处理在进行刻蚀之前,需要对晶圆进行清洗和预处理,以去除表面的杂质和自然氧化层。清洗过程通常包括多个步骤,如使用化学溶剂清洗、超纯水冲洗等,确保晶圆表面干净、平整。2、光刻光刻是刻蚀工艺的前序步骤。在晶圆表面涂上一层光刻胶,然后使用光刻机将设计好的图案曝光在光刻胶上。曝光后的光刻胶在显影液中进行处理,未曝光的部分被溶解掉,露出晶圆表面需要刻蚀的区域。3、刻蚀根据选择的刻蚀方式(湿法或干法),将晶圆放入相应的刻蚀设备中进行刻蚀。在刻蚀过程中,需要严格控制刻蚀的时间、温度、压力、气体流量(针对干法刻蚀)等参数,以确保刻蚀的效果符合要求。4、后处理刻蚀完成后,需要对晶圆进行清洗和检测。清洗过程主要是去除残留的光刻胶和刻蚀产物,检测过程包括对刻蚀深度、图案尺寸和形状等参数的测量,确保刻蚀后的图案符合设计要求。

六、“刻蚀”工艺的流程1、预处理在进行刻蚀之前,需要对晶圆进行清洗和预处理,以去除表面的杂质和自然氧化层。清洗过程通常包括多个步骤,如使用化学溶剂清洗、超纯水冲洗等,确保晶圆表面干净、平整。2、光刻光刻是刻蚀工艺的前序步骤。在晶圆表面涂上一层光刻胶,然后使用光刻机将设计好的图案曝光在光刻胶上。曝光后的光刻胶在显影液中进行处理,未曝光的部分被溶解掉,露出晶圆表面需要刻蚀的区域。3、刻蚀根据选择的刻蚀方式(湿法或干法),将晶圆放入相应的刻蚀设备中进行刻蚀。在刻蚀过程中,需要严格控制刻蚀的时间、温度、压力、气体流量(针对干法刻蚀)等参数,以确保刻蚀的效果符合要求。4、后处理刻蚀完成后,需要对晶圆进行清洗和检测。清洗过程主要是去除残留的光刻胶和刻蚀产物,检测过程包括对刻蚀深度、图案尺寸和形状等参数的测量,确保刻蚀后的图案符合设计要求。 七、“刻蚀”工艺的参数1、刻蚀速率(Etch Rate)定义:单位时间内材料被去除的厚度(如 nm/min 或 Å/min)。影响因素:干法:等离子体功率、气体流量、压力、离子能量。湿法:溶液浓度、温度、搅拌速度。重要性:速率过高可能导致过刻蚀,过低则影响生产效率。2、刻蚀均匀性(Uniformity)定义:刻蚀速率在晶圆表面或图形间的差异(通常用百分比表示,如 ±5%)。影响因素:干法:等离子体分布、气体流动均匀性、腔体设计。湿法:溶液搅拌、晶圆旋转、浸泡时间。关键指标:片内均匀性(WIW)和片间均匀性(WTW)。3、选择性(Selectivity)定义:刻蚀目标材料与掩膜或下层材料的刻蚀速率比(如 Si:SiO₂ = 50:1)。影响因素:干法:气体化学(如 Cl₂ 对 Si 高选择性)、离子能量。湿法:溶液成分(如 HF 对 SiO₂ 高选择性)。重要性:高选择性保护掩膜和底层结构,减少损伤。

七、“刻蚀”工艺的参数1、刻蚀速率(Etch Rate)定义:单位时间内材料被去除的厚度(如 nm/min 或 Å/min)。影响因素:干法:等离子体功率、气体流量、压力、离子能量。湿法:溶液浓度、温度、搅拌速度。重要性:速率过高可能导致过刻蚀,过低则影响生产效率。2、刻蚀均匀性(Uniformity)定义:刻蚀速率在晶圆表面或图形间的差异(通常用百分比表示,如 ±5%)。影响因素:干法:等离子体分布、气体流动均匀性、腔体设计。湿法:溶液搅拌、晶圆旋转、浸泡时间。关键指标:片内均匀性(WIW)和片间均匀性(WTW)。3、选择性(Selectivity)定义:刻蚀目标材料与掩膜或下层材料的刻蚀速率比(如 Si:SiO₂ = 50:1)。影响因素:干法:气体化学(如 Cl₂ 对 Si 高选择性)、离子能量。湿法:溶液成分(如 HF 对 SiO₂ 高选择性)。重要性:高选择性保护掩膜和底层结构,减少损伤。 4、各向异性(Anisotropy)定义:刻蚀的垂直方向与横向刻蚀的比例(完全各向异性 = 无横向刻蚀)。影响因素:干法:离子轰击方向(如 RIE)、侧壁钝化(如 Bosch 工艺)。湿法:通常各向同性(横向钻蚀明显)。应用场景:高深宽比结构(如 TSV、FinFET)需高各向异性。5、刻蚀剖面(Etch Profile)定义:刻蚀后结构的侧壁形貌(如垂直、锥形、倒梯形)。关键参数:侧壁角度:90°为理想垂直剖面。粗糙度:侧壁光滑度(影响器件性能)。控制方法:调整离子能量、气体化学、温度。6、负载效应(Loading Effect)定义:刻蚀速率因图形密度或面积不同而变化的现象。类型:宏观负载效应:晶圆间刻蚀速率差异。微观负载效应:图形密集区与稀疏区速率差异。解决方案:优化等离子体均匀性、调节气体流量。7、残留物与聚合物(Residue/Polymer)定义:刻蚀后残留的副产物(如碳氟聚合物)。来源:干法:气体反应不完全(如 CF₄ 刻蚀 Si 产生 SiF₄ 和 CₓFᵧ)。湿法:金属离子残留(如 Al 刻蚀后 Cu 污染)。清除方法:O₂ 等离子体灰化、湿法清洗(RCA)。下面是干法刻蚀和湿法刻蚀的关键参数控制表格:

4、各向异性(Anisotropy)定义:刻蚀的垂直方向与横向刻蚀的比例(完全各向异性 = 无横向刻蚀)。影响因素:干法:离子轰击方向(如 RIE)、侧壁钝化(如 Bosch 工艺)。湿法:通常各向同性(横向钻蚀明显)。应用场景:高深宽比结构(如 TSV、FinFET)需高各向异性。5、刻蚀剖面(Etch Profile)定义:刻蚀后结构的侧壁形貌(如垂直、锥形、倒梯形)。关键参数:侧壁角度:90°为理想垂直剖面。粗糙度:侧壁光滑度(影响器件性能)。控制方法:调整离子能量、气体化学、温度。6、负载效应(Loading Effect)定义:刻蚀速率因图形密度或面积不同而变化的现象。类型:宏观负载效应:晶圆间刻蚀速率差异。微观负载效应:图形密集区与稀疏区速率差异。解决方案:优化等离子体均匀性、调节气体流量。7、残留物与聚合物(Residue/Polymer)定义:刻蚀后残留的副产物(如碳氟聚合物)。来源:干法:气体反应不完全(如 CF₄ 刻蚀 Si 产生 SiF₄ 和 CₓFᵧ)。湿法:金属离子残留(如 Al 刻蚀后 Cu 污染)。清除方法:O₂ 等离子体灰化、湿法清洗(RCA)。下面是干法刻蚀和湿法刻蚀的关键参数控制表格: 八、“刻蚀”工艺技术的详细介绍以下就是要跟大家分享的具体内容,希望感兴趣的朋友可以加入我的“知识星球”,一起多多交流学习:

八、“刻蚀”工艺技术的详细介绍以下就是要跟大家分享的具体内容,希望感兴趣的朋友可以加入我的“知识星球”,一起多多交流学习:

因为本PPT章节太多,剩下部分如有朋友有需要,可加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!文末有加入“星球”方式,欢迎加入后一起交流学习。九、“刻蚀”工艺当前面对的挑战1、3D NAND的高深宽比(HAR)刻蚀挑战(1)深孔/深槽刻蚀128层及以上3D NAND需刻蚀深宽比>60:1的通道孔(如7μm深、<100nm宽),离子和反应物传输困难,易导致刻蚀不完全或侧壁扭曲。(2)掩膜消耗与选择比高能离子轰击加速掩膜(如碳硬掩膜)消耗,需开发新型掩膜材料或优化刻蚀气体配比。2、先进制程的高精度要求(1)纳米级刻蚀控制在5nm及以下制程中,刻蚀精度需达到原子级别(如<1nm),传统刻蚀方法难以满足要求。原子层刻蚀(ALE)虽能实现单原子层去除,但工艺复杂且成本高昂。(2)关键尺寸(CD)均匀性多重曝光技术(如EUV+SAQP)要求刻蚀后线宽误差控制在±0.5nm以内,否则影响器件性能。3、国产化技术瓶颈(1)高端设备依赖进口中国刻蚀设备的国产化率在2025年已达到约20%,但7nm以下刻蚀设备仍由泛林(Lam)、东京电子(TEL)垄断,国产设备(如中微CCP)在5nm验证中但市占率不足10%,(2)关键零部件卡脖子射频电源、真空泵等核心部件依赖欧美日供应链。

因为本PPT章节太多,剩下部分如有朋友有需要,可加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!文末有加入“星球”方式,欢迎加入后一起交流学习。九、“刻蚀”工艺当前面对的挑战1、3D NAND的高深宽比(HAR)刻蚀挑战(1)深孔/深槽刻蚀128层及以上3D NAND需刻蚀深宽比>60:1的通道孔(如7μm深、<100nm宽),离子和反应物传输困难,易导致刻蚀不完全或侧壁扭曲。(2)掩膜消耗与选择比高能离子轰击加速掩膜(如碳硬掩膜)消耗,需开发新型掩膜材料或优化刻蚀气体配比。2、先进制程的高精度要求(1)纳米级刻蚀控制在5nm及以下制程中,刻蚀精度需达到原子级别(如<1nm),传统刻蚀方法难以满足要求。原子层刻蚀(ALE)虽能实现单原子层去除,但工艺复杂且成本高昂。(2)关键尺寸(CD)均匀性多重曝光技术(如EUV+SAQP)要求刻蚀后线宽误差控制在±0.5nm以内,否则影响器件性能。3、国产化技术瓶颈(1)高端设备依赖进口中国刻蚀设备的国产化率在2025年已达到约20%,但7nm以下刻蚀设备仍由泛林(Lam)、东京电子(TEL)垄断,国产设备(如中微CCP)在5nm验证中但市占率不足10%,(2)关键零部件卡脖子射频电源、真空泵等核心部件依赖欧美日供应链。 十、“刻蚀”工艺未来的发展刻蚀技术就像医生手中的手术刀,其技术演化直接决定摩尔定律乃至后摩尔时代芯片制造的发展趋势,新型材料和智能化Al的运用将形成新的驱动力推动刻蚀技术发展。原子层刻蚀(ALE):单原子层精度控制。AI工艺优化:通过大数据实时调节刻蚀参数。新型等离子体源/新型气体化学:如超低温ICP(-50°C)减少损伤,NF₃/Ar混合气体提升SiC刻蚀速率(>2μm/min)。总之,由于“刻蚀”工艺技术是紧随光刻技术而来,它涉及使用化学或物理方法去除硅片上多余的材料,以形成所需的图案。这一过程中,精确控制刻蚀的深度和位置至关重要。刻蚀技术的发展同样对提高芯片质量和性能起着关键作用。

十、“刻蚀”工艺未来的发展刻蚀技术就像医生手中的手术刀,其技术演化直接决定摩尔定律乃至后摩尔时代芯片制造的发展趋势,新型材料和智能化Al的运用将形成新的驱动力推动刻蚀技术发展。原子层刻蚀(ALE):单原子层精度控制。AI工艺优化:通过大数据实时调节刻蚀参数。新型等离子体源/新型气体化学:如超低温ICP(-50°C)减少损伤,NF₃/Ar混合气体提升SiC刻蚀速率(>2μm/min)。总之,由于“刻蚀”工艺技术是紧随光刻技术而来,它涉及使用化学或物理方法去除硅片上多余的材料,以形成所需的图案。这一过程中,精确控制刻蚀的深度和位置至关重要。刻蚀技术的发展同样对提高芯片质量和性能起着关键作用。 -----End-----免责声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

-----End-----免责声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏