我们来深入探讨一下CPU读内存这个看似简单,实则充满“门道”的操作。确实,很多人会简单地将它理解为CPU向内存发出请求,然后数据就“飞”过来了。但底层的机制远比这复杂,其中"指令"和"缓存"是两个至关重要的核心要素。

"一、 CPU读内存的基本流程(理想化模型)"

为了便于理解,我们先看一个简化的流程:

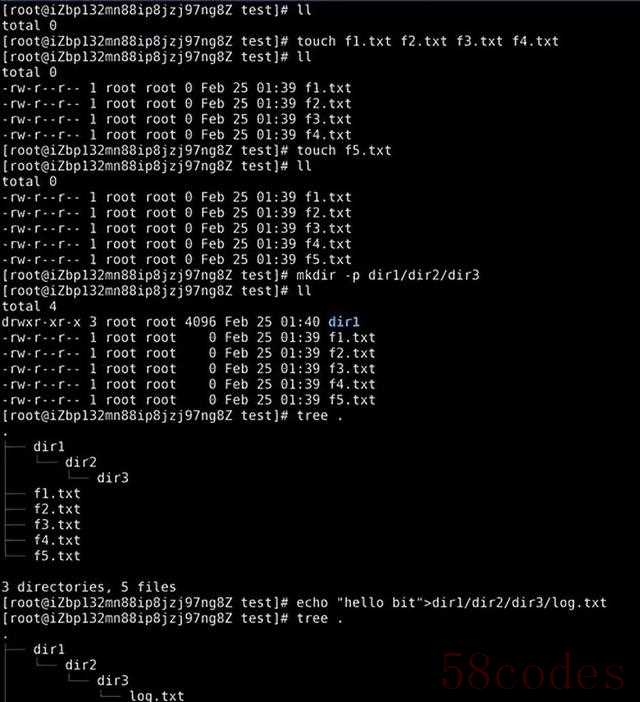

1. "指令触发 (Instruction Triggering):" CPU执行某条指令(比如 `MOV AX, [1000H]`),这条指令明确要求CPU读取内存地址`1000H`处的数据,并将读取到的数据存入CPU内部寄存器`AX`。

2. "地址生成 (Address Generation):" CPU的地址生成单元(AGU)根据指令中的地址(或通过寻址方式计算得出)生成内存地址`1000H`。

3. "内存请求 (Memory Request):" CPU通过总线(Bus)向内存控制器(Memory Controller)发出读请求,告知需要读取地址`1000H`的数据。

4. "内存响应 (Memory Response):" 内存控制器接收请求,找到物理内存中地址`1000H`的位置,将对应的数据读取出来。

5. "数据返回 (Data Return):" 内存控制器通过总线将数据`[1000H]`送回CPU。

6.

相关内容:

“电脑又卡了?

”——八成不是内存不够,是CPU在内存里绕远路。

DDR5已经普及,可很多人升级后依旧卡成PPT。

问题不在容量,在CPU怎么“拿”数据。

拿得慢,再贵的条子也白搭。

先说缓存。

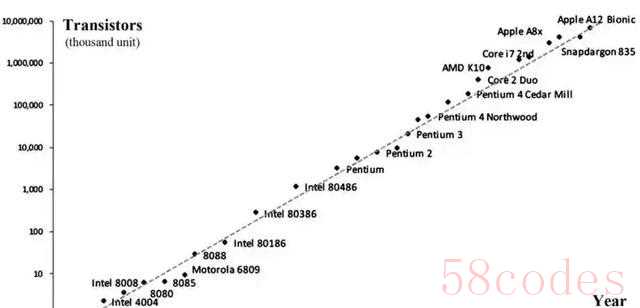

AMD Zen4把L3怼到192MB,像把超市开在家门口;Intel MeteorLake却把缓存拆成几间便利店,谁离得近谁快。

两种思路,一个堆量,一个拼调度。

实测剪4K视频,Zen4X3D比同频Zen4快18%,就是缓存猛砸出来的。

DDR5带宽看着爽,延迟却涨了。

DDR4-3200 CL16延迟约10ns,DDR5-6000 CL36飙到12ns。

CPU得靠更聪明的预取算法补锅。

苹果M2的统一内存架构直接把CPU、GPU绑在一起,数据不用来回搬家,剪片子导出快得离谱,代价是内存焊死,坏了得换主板——苹果式“省时省钱二选一”。

AI也在帮倒忙。

NVIDIA Hopper的TransformerEngine会提前把下一批参数搬进缓存,猜错就全浪费带宽。

实测Stable Diffusion出图,开不开这功能能差3秒,玄学得很。

更离谱的是Intel Optane,插在内存槽里当硬盘用。

开机像SSD,跑数据库又像内存,价格介于两者之间,定位尴尬。

适合那种“内存128G还不够,上256G又太贵”的怪需求。

多核同步也卷疯了。

AMD Zen4c把核间通信延迟压到15ns,比上一代少一半。

跑渲染农场,16核Zen4c能顶20核Zen3。代价是单核性能缩水,打游戏别碰。

安全补丁更吃性能。

Intel的TME内存加密一开,部分场景掉速10%。

ARMv9的MTE防漏洞,但老软件直接报错。

升级前得想清楚:要安全还是速度?

给普通人三条建议:

1. 剪视频/跑AI直接上3D V-Cache,缓存比频率管用。

2. 多开虚拟机先查主板QVL,DDR5兼容性玄学,插错条子直接黑屏。

3.电脑突然卡顿,先关浏览器再开任务管理器,八成是某个核的缓存被Chrome吃光了。

最后泼盆冷水:DDR5-8000、HBM3听着爽,但Win11的内存调度还停留在“能用就行”。

硬件冲太快,软件在拖后腿——就像给拖拉机装火箭发动机,声音大,跑不快。

微信扫一扫打赏

微信扫一扫打赏

支付宝扫一扫打赏

支付宝扫一扫打赏